### **ANNEXE A1**

### MC14504B

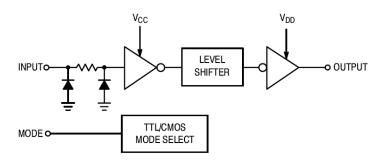

## Hex Level Shifter for TTL to CMOS or CMOS to CMOS

The MC14504B is a hex non–inverting level shifter using CMOS technology. The level shifter will shift a TTL signal to CMOS logic levels for any CMOS supply voltage between 5 and 15 volts. A control input also allows interface from CMOS to CMOS at one logic level to another logic level: Either up or down level translating is accomplished by selection of power supply levels  $V_{DD}$  and  $V_{CC}$ . The  $V_{CC}$  level sets the input signal levels while  $V_{DD}$  selects the output voltage levels.

- UP Translates from a Low to a High Voltage or DOWN Translates from a High to a Low Voltage

- Input Threshold Can Be Shifted for TTL Compatibility

- No Sequencing Required on Power Supplies or Inputs for Power Up or Power Down

- $\bullet~$  3 to 18 Vdc Operation for  $V_{DD}$  and  $V_{CC}$

- Diode Protected Inputs to V<sub>SS</sub>

- Capable of Driving Two Low-Power TTL Loads or One Low-Power Schottky TTL Load Over the Rated Temperature Range

#### **MAXIMUM RATINGS** (Voltages Referenced to $V_{SS}$ ) (Note 2.)

| Symbol                             | Parameter                                            | Value                         | Unit |

|------------------------------------|------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>                    | DC Supply Voltage Range                              | -0.5 to +18.0                 | V    |

| $V_{DD}$                           | DC Supply Voltage Range                              | -0.5 to +18.0                 | V    |

| V <sub>in</sub>                    | Input Voltage Range<br>(DC or Transient)             | -0.5 to +18.0                 | ٧    |

| V <sub>out</sub>                   | Output Voltage Range<br>(DC or Transient)            | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| I <sub>in</sub> , I <sub>out</sub> | Input or Output Current<br>(DC or Transient) per Pin | ±10                           | mA   |

| P <sub>D</sub>                     | Power Dissipation,<br>per Package (Note 3.)          | 500                           | mW   |

| T <sub>A</sub>                     | Ambient Temperature Range                            | -55 to +125                   | °C   |

| T <sub>stg</sub>                   | Storage Temperature Range                            | -65 to +150                   | °C   |

| TL                                 | Lead Temperature<br>(8–Second Soldering)             | 260                           | °C   |

- Maximum Ratings are those values beyond which damage to the device may occur.

- Temperature Derating: Plastic "P and D/DW" Packages: – 7.0 mW/°C From 65°C To 125°C

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs must be left open.

### **ON Semiconductor**

http://onsemi.com

#### MARKING DIAGRAMS

PDIP-16 P SUFFIX CASE 648

SOIC-16 D SUFFIX CASE 751B

TSSOP-16 DT SUFFIX CASE 948F

SOEIAJ-16 F SUFFIX CASE 966

A = Assembly Location

WL, L = Wafer Lot YY, Y = Year WW, W = Work Week

### ORDERING INFORMATION

| Device      | Package   | Shipping         |  |  |  |  |  |

|-------------|-----------|------------------|--|--|--|--|--|

| MC14504BCP  | PDIP-16   | 2000/Box         |  |  |  |  |  |

| MC14504BD   | SOIC-16   | 48/Rail          |  |  |  |  |  |

| MC14504BDR2 | SOIC-16   | 2500/Tape & Reel |  |  |  |  |  |

| MC14504BDT  | TSSOP-16  | 96/Rail          |  |  |  |  |  |

| MC14504BF   | SOEIAJ-16 | See Note 1.      |  |  |  |  |  |

| MC14504BFEL | SOEIAJ-16 | See Note 1.      |  |  |  |  |  |

For ordering information on the EIAJ version of the SOIC packages, please contact your local ON Semiconductor representative.

### MC14504B

### LOGIC DIAGRAM

| Mode Select          | Input Logic<br>Levels | Output Logic<br>Levels |

|----------------------|-----------------------|------------------------|

| 1 (V <sub>CC</sub> ) | TTL                   | CMOS                   |

| 0 (V <sub>SS</sub> ) | CMOS                  | CMOS                   |

1/6 of package shown.

### **ANNEXE A2**

CD4049UB, CD4050B

Data sheet acquired from Harris Semiconductor SCHS046A

August 1998 - Revised May 1999

### CMOS Hex Buffer/Converters

The CD4049UB and CD4050B devices are inverting and non-inverting hex buffers, respectively, and feature logic-level conversion using only one supply voltage (V<sub>CC</sub>). The input-signal high level (V<sub>IH</sub>) can exceed the V<sub>CC</sub> supply voltage when these devices are used for logic-level conversions. These devices are intended for use as CMOS to DTL/TTL converters and can drive directly two DTL/TTL loads. (V<sub>CC</sub> = 5V, V<sub>OL</sub>  $\leq$  0.4V, and I<sub>OL</sub>  $\geq$  3.3mA.)

The CD4049UB and CD4050B are designated as replacements for CD4009UB and CD4010B, respectively. Because the CD4049UB and CD4050B require only one power supply, they are preferred over the CD4009UB and CD4010B and should be used in place of the CD4009UB and CD4010B in all inverter, current driver, or logic-level conversion applications. In these applications the CD4049UB and CD4050B are pin compatible with the CD4009UB and CD4010B respectively, and can be substituted for these devices in existing as well as in new designs. Terminal No. 16 is not connected internally on the CD4049UB or CD4050B, therefore, connection to this terminal is of no consequence to circuit operation. For applications not requiring high sink-current or voltage conversion, the CD4069UB Hex Inverter is recommended.

### Features

- CD4049UB Inverting

- · CD4050B Non-Inverting

- · High Sink Current for Driving 2 TTL Loads

- · High-To-Low Level Logic Conversion

- 100% Tested for Quiescent Current at 20V

- Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and 25°C

- · 5V, 10V and 15V Parametric Ratings

### Applications

- · CMOS to DTL/TTL Hex Converter

- · CMOS Current "Sink" or "Source" Driver

- · CMOS High-To-Low Logic Level Converter

### Ordering Information

| PART NUMBER | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE      | PKG.<br>NO. |

|-------------|----------------------------------|--------------|-------------|

| CD4049UBE   | -55 to 125                       | 16 Ld PDIP   | E16.3       |

| CD4050BE    | -55 to 125                       | 16 Ld PDIP   | E16.3       |

| CD4049UBF   | -55 to 125                       | 16 Ld CERDIP | F16.3       |

| CD4050BF    | -55 to 125                       | 16 Ld CERDIP | F16.3       |

| CD4050BM    | -55 to 125                       | 16 Ld SOIC   | M16.3       |

NOTE: Wafer and die for this part number is available which meets all electrical specifications. Please contact your local sales office or customer service for ordering information.

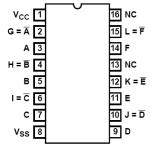

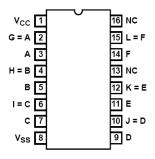

### **Pinouts**

#### CD4049UB (PDIP, CERDIP) TOP VIEW

### CD4050B (PDIP, CERDIP, SOIC) TOP VIEW

### CD4049UB, CD4050B

#### **Absolute Maximum Ratings** Thermal Information $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W) Supply Voltage (V+ to V-).....-0.5V to 20V Thermal Resistance (Typical, Note 1) PDIP Package ..... CERDIP Package..... 130 55 100 N/A **Operating Conditions** . . . .150°C Maximum Junction Temperature (Plastic Package) ... Temperature Range . . . . . . . . . . . . -55°C to 125°C Maximum Storage Temperature Range . . . . . . -65°C to 150°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

(SOIC - Lead Tips Only)

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **DC Electrical Specifications**

|                                          |                    |                        |                     | LIMITS AT INDICATED TEMPERATURE (°C) |       |       |       |       |      |      |       |

|------------------------------------------|--------------------|------------------------|---------------------|--------------------------------------|-------|-------|-------|-------|------|------|-------|

|                                          | TES                | TEST CONDITIONS        |                     |                                      |       |       |       |       | 25   |      |       |

| PARAMETER                                | V <sub>O</sub> (V) | V <sub>IN</sub><br>(V) | V <sub>CC</sub> (V) | -55                                  | -40   | 85    | 125   | MIN   | TYP  | MAX  | UNITS |

| Quiescent Device Current                 | -                  | 0,5                    | 5                   | 1                                    | 1     | 30    | 30    | -     | 0.02 | 1    | μА    |

| I <sub>DD</sub> (Max)                    | -                  | 0,10                   | 10                  | 2                                    | 2     | 60    | 60    | -     | 0.02 | 2    | μА    |

|                                          | -                  | 0,15                   | 15                  | 4                                    | 4     | 120   | 120   | -     | 0.02 | 4    | μА    |

|                                          | -                  | 0,20                   | 20                  | 20                                   | 20    | 600   | 600   | -     | 0.04 | 20   | μА    |

| Output Low (Sink) Current                | 0.4                | 0,5                    | 4.5                 | 3.3                                  | 3.1   | 2.1   | 1.8   | 2.6   | 5.2  | -    | mA    |

| I <sub>OL</sub> (Min)                    | 0.4                | 0,5                    | 5                   | 4                                    | 3.8   | 2.9   | 2.4   | 3.2   | 6.4  | -    | mA    |

|                                          | 0.5                | 0,10                   | 10                  | 10                                   | 9.6   | 6.6   | 5.6   | 8     | 16   | -    | mA    |

|                                          | 1.5                | 0,15                   | 15                  | 26                                   | 25    | 20    | 18    | 24    | 48   | -    | mA    |

| Output High (Source) Current             | 4.6                | 0,5                    | 5                   | -0.81                                | -0.73 | -0.58 | -0.48 | -0.65 | -1.2 | -    | mA    |

| I <sub>OH</sub> (Min)                    | 2.5                | 0,5                    | 5                   | -2.6                                 | -2.4  | -1.9  | -1.55 | -2.1  | -3.9 | -    | mA    |

|                                          | 9.5                | 0,10                   | 10                  | -2.0                                 | -1.8  | -1.35 | -1.18 | -1.65 | -3.0 | -    | mA    |

|                                          | 13.5               | 0,15                   | 15                  | -5.2                                 | -4.8  | -3.5  | -3.1  | -4.3  | -8.0 | -    | mA    |

| Out Voltage Low Level                    | -                  | 0,5                    | 5                   | 0.05                                 | 0.05  | 0.05  | 0.05  | -     | 0    | 0.05 | V     |

| V <sub>OL</sub> (Max)                    | -                  | 0,10                   | 10                  | 0.05                                 | 0.05  | 0.05  | 0.05  | -     | 0    | 0.05 | V     |

|                                          | -                  | 0,15                   | 5                   | 0.05                                 | 0.05  | 0.05  | 0.05  | -     | 0    | 0.05 | V     |

| Output Voltage High Level                | -                  | 0,5                    | 5                   | 4.95                                 | 4.95  | 4.95  | 4.95  | 4.95  | 5    | -    | V     |

| V <sub>OH</sub> (Min)                    | -                  | 0,10                   | 10                  | 9.95                                 | 9.95  | 9.95  | 9.95  | 9.95  | 10   | -    | V     |

|                                          | -                  | 0,15                   | 15                  | 14.95                                | 14.95 | 14.95 | 14.95 | 14.95 | 15   | -    | V     |

| Input Low Voltage, V <sub>IL</sub> (Max) | 4.5                | -                      | 5                   | 1                                    | 1     | 1     | 1     | -     | -    | 1    | V     |

| CD4049UB                                 | 9                  | -                      | 10                  | 2                                    | 2     | 2     | 2     | -     | -    | 2    | V     |

|                                          | 13.5               | -                      | 15                  | 2.5                                  | 2.5   | 2.5   | 2.5   | -     | -    | 2.5  | V     |

| Input Low Voltage, V <sub>IL</sub> (Max) | 0.5                | -                      | 5                   | 1.5                                  | 1.5   | 1.5   | 1.5   | -     | -    | 1.5  | V     |

| CD4050B                                  | 1                  | -                      | 10                  | 3                                    | 3     | 3     | 3     | -     | -    | 3    | V     |

|                                          | 1.5                | -                      | 15                  | 4                                    | 4     | 4     | 4     | -     | -    | 4    | V     |

| Input High Voltage, V <sub>IH</sub> Min  | 0.5                | -                      | 5                   | 4                                    | 4     | 4     | 4     | 4     | -    | -    | V     |

| CD4049UB                                 | 1                  | -                      | 10                  | 8                                    | 8     | 8     | 8     | 8     | -    | -    | V     |

|                                          | 1.5                | -                      | 15                  | 12.5                                 | 12.5  | 12.5  | 12.5  | 12.5  | -    | -    | V     |

### **ANNEXE B1**

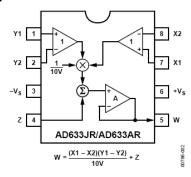

Data Sheet AD633

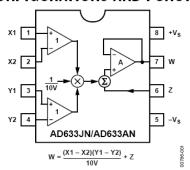

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 2. 8-Lead PDIP

Figure 3. 8-Lead SOIC

Table 4. 8-Lead PDIP Pin Function Descriptions

| The state of the s |          |                                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|--|--|--|

| Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mnemonic | Description                       |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X1       | X Multiplicand Noninverting Input |  |  |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X2       | X Multiplicand Inverting Input    |  |  |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y1       | Y Multiplicand Noninverting Input |  |  |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y2       | Y Multiplicand Inverting Input    |  |  |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -Vs      | Negative Supply Rail              |  |  |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z        | Summing Input                     |  |  |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W        | Product Output                    |  |  |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | +Vs      | Positive Supply Rail              |  |  |  |

Table 5. 8-Lead SOIC Pin Function Descriptions

| Pin No. | Mnemonic | Description                       |

|---------|----------|-----------------------------------|

| 1       | Y1       | Y Multiplicand Noninverting Input |

| 2       | Y2       | Y Multiplicand Inverting Input    |

| 3       | -Vs      | Negative Supply Rail              |

| 4       | Z        | Summing Input                     |

| 5       | W        | Product Output                    |

| 6       | +Vs      | Positive Supply Rail              |

| 7       | X1       | X Multiplicand Noninverting Input |

| 8       | X2       | X Multiplicand Inverting Input    |

Data Sheet AD633

### **SPECIFICATIONS**

$T_A = 25$ °C,  $V_S = \pm 15$  V,  $R_L \ge 2$  k $\Omega$ .

Table 1.

|                          |                                                       |                 | AD633J, AD633A               |                  |              |

|--------------------------|-------------------------------------------------------|-----------------|------------------------------|------------------|--------------|

| Parameter                | Conditions                                            | Min             | Тур                          | Max              | Unit         |

| TRANSFER FUNCTION        |                                                       |                 | (X1-X2)(Y)                   | 1 – Y2)          |              |

|                          |                                                       | W               | $V = \frac{V}{10 \text{ V}}$ | +Z               |              |

| MULTIPLIER PERFORMANCE   |                                                       |                 |                              | •                |              |

| Total Error              | $-10 \text{ V} \leq \text{X, Y} \leq +10 \text{ V}$   |                 | ±1                           | ±21              | % full scale |

| TMIN TO TMAX             |                                                       |                 | ±3                           |                  | % full scale |

| Scale Voltage Error      | SF = 10.00 V nominal                                  |                 | ±0.25%                       |                  | % full scale |

| Supply Rejection         | $V_S = \pm 14  \text{V} \text{ to } \pm 16  \text{V}$ |                 | ±0.01                        |                  | % full scale |

| Nonlinearity, X          | $X = \pm 10 \text{ V}, Y = +10 \text{ V}$             |                 | ±0.4                         | ±11              | % full scale |

| Nonlinearity, Y          | $Y = \pm 10 \text{ V}, X = +10 \text{ V}$             |                 | ±0.1                         | ±0.41            | % full scale |

| X Feedthrough            | Y nulled, $X = \pm 10 \text{ V}$                      |                 | ±0.3                         | ±11              | % full scale |

| Y Feedthrough            | X nulled, $Y = \pm 10 \text{ V}$                      |                 | ±0.1                         | ±0.41            | % full scale |

| Output Offset Voltage    |                                                       |                 | ±5                           | ±501             | mV           |

| DYNAMICS                 |                                                       |                 | •                            |                  |              |

| Small Signal Bandwidth   | $V_0 = 0.1 \text{ V rms}$                             |                 | 1                            |                  | MHz          |

| Slew Rate                | $V_0 = 20 \text{ V p-p}$                              |                 | 20                           |                  | V/µs         |

| Settling Time to 1%      | $\Delta V_0 = 20 \text{ V}$                           |                 | 2                            |                  | μs           |

| OUTPUT NOISE             |                                                       |                 |                              | •                |              |

| Spectral Density         |                                                       |                 | 0.8                          |                  | μV/√Hz       |

| Wideband Noise           | f = 10  Hz to  5  MHz                                 |                 | 1                            |                  | mV rms       |

|                          | f = 10  Hz to  10  kHz                                |                 | 90                           |                  | μV rms       |

| OUTPUT                   |                                                       |                 |                              |                  |              |

| Output Voltage Swing     |                                                       | ±111            |                              |                  | V            |

| Short Circuit Current    | $R_L = 0 \Omega$                                      |                 | 30                           | 401              | mA           |

| INPUT AMPLIFIERS         |                                                       |                 |                              |                  |              |

| Signal Voltage Range     | Differential                                          | ±101            |                              |                  | V            |

|                          | Common mode                                           | ±101            |                              |                  | V            |

| Offset Voltage (X, Y)    |                                                       |                 | ±5                           | ±301             | mV           |

| CMRR (X, Y)              | $V_{CM} = \pm 10 \text{ V, } f = 50 \text{ Hz}$       | 60 <sup>1</sup> | 80                           |                  | dB           |

| Bias Current $(X, Y, Z)$ |                                                       |                 | 0.8                          | 2.0 <sup>1</sup> | μΑ           |

| Differential Resistance  |                                                       |                 | 10                           |                  | ΜΩ           |

| POWER SUPPLY             |                                                       |                 |                              | -                |              |

| Supply Voltage           |                                                       |                 |                              |                  |              |

| Rated Performance        |                                                       |                 | ±15                          |                  | V            |

| Operating Range          |                                                       | ±81             |                              | ±181             | V            |

| Supply Current           | Quiescent                                             |                 | 4                            | 6 <sup>1</sup>   | mA           |

<sup>&</sup>lt;sup>1</sup> This specification was tested on all production units at electrical test. Results from those tests are used to calculate outgoing quality levels. All minimum and maximum specifications are guaranteed; however, only this specification was tested on all production units.

### **ANNEXE C1**

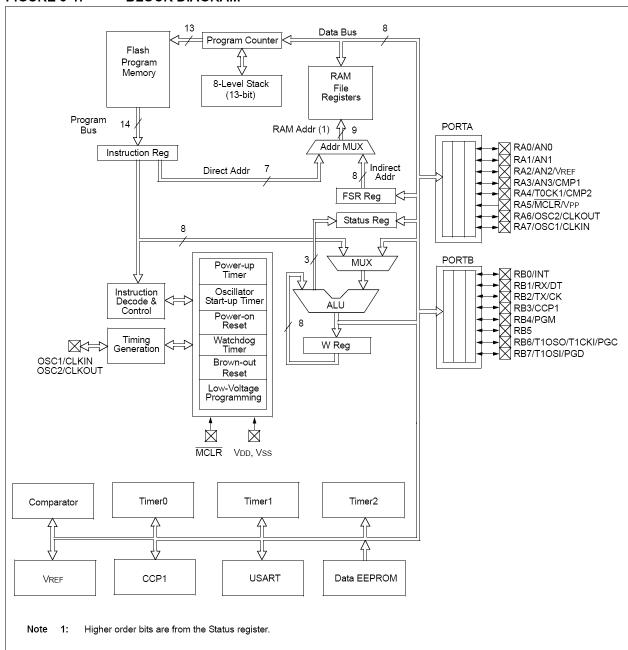

### PIC16F627A/628A/648A

FIGURE 3-1: BLOCK DIAGRAM

### 4.2.2.1 Status Register

The Status register, shown in Register 4-1, contains the arithmetic status of the ALU; the Reset status and the bank select bits for data memory (SRAM).

The Status register can be the destination for any instruction, like any other register. If the Status register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are non-writable. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the Status register as "000uu1uu" (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the Status register because these instructions do not affect any Status bit. For other instructions, not affecting any Status bits, see the "Instruction Set Summary".

Note: The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | O     |

| bit 7 | •     |       |     |     |       | •     | bit 0 |

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h-1FFh)

0 = Bank 0, 1 (00h-FFh)

bit 6-5 **RP<1:0>**: Register Bank Select bits (used for direct addressing)

00 = Bank 0 (00h-7Fh)

01 = Bank 1 (80h-FFh)

10 = Bank 2 (100h-17Fh)

11 = Bank 3 (180h-1FFh)

bit 4 **TO**: Time Out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time out occurred

bit 3 **PD**: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 **Z**: Zero bit

1 = The result of an arithmetic or logic operation is zero

o = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for Borrow the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

**Note:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.2 OPTION Register

The Option register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1). See Section 6.3.1 "Switching Prescaler Assignment".

### REGISTER 4-2: OPTION\_REG - OPTION REGISTER (ADDRESS: 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

o = Interrupt on falling edge of RB0/INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI/CMP2 pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI/CMP2 pin

0 = Increment on low-to-high transition on RA4/T0CKI/CMP2 pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1:128    |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 "PIE1 Register" and Section 4.2.2.5 "PIR1 Register" for a description of the comparator enable and flag bits.

Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON - INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Note:

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all un-masked interrupts

o = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all un-masked peripheral interrupts

o = Disables all peripheral interrupts

bit 5 **T0IE**: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

o = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

o = Disables the RB port change interrupt

bit 2 T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

o = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

o = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = When at least one of the RB<7:4> pins changes state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.5 PIR1 Register

bit 4

This register contains interrupt flag bits.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 4-5: PIR1 – PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

| R/W-0 | R/W-0 | R-0  | R-0  | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|------|------|-----|--------|--------|--------|

| EEIF  | CMIF  | RCIF | TXIF | _   | CCP1IF | TMR2IF | TMR1IF |

| bit 7 | •     | •    | •    | •   |        | ,      | bit 0  |

bit 7 **EEIF:** EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation has not completed or has not been started

bit 6 **CMIF**: Comparator Interrupt Flag bit

1 = Comparator output has changed

0 = Comparator output has not changed

bit 5 RCIF: USART Receive Interrupt Flag bit

1 = The USART receive buffer is full

0 = The USART receive buffer is empty

TXIF: USART Transmit Interrupt Flag bit

1 = The USART transmit buffer is empty

o = The USART transmit buffer is full

bit 3 **Unimplemented**: Read as '0'

bit 2 CCP1IF: CCP1 Interrupt Flag bit

#### Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

o = No TMR1 register capture occurred

#### Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

#### PWM Mode

Unused in this mode

bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

o = TMR1 register did not overflow

# Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

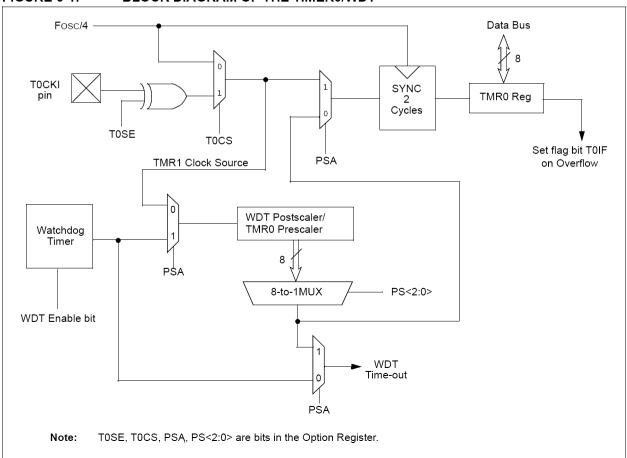

### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

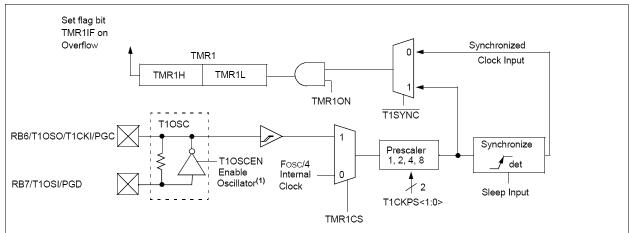

### 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 Interrupt, if enabled, is generated on overflow of the TMR1 register pair which latches the interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing the Timer1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, the TMR1 register pair value increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (Section 9.0 "Capture/Compare/PWM (CCP) Module"). Register 7-1 shows the Timer1 control register.

For the PIC16F627A/628A/648A, when the Timer1 oscillator is enabled (T10SCEN is set), the RB7/T10SI/PGD and RB6/T10SO/T1CKI/PGC pins become inputs. That is, the TRISB<7:6> value is ignored.

### REGISTER 7-1: T1CON – TIMER1 CONTROL REGISTER (ADDRESS: 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     | _   | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 | •   |         |         |         | •      |        | bit 0  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value

01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled 0 = Oscillator is shut off<sup>(1)</sup>

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

**TMR1CS = 1**

1 = Do not synchronize external clock input

0 = Synchronize external clock input

<u>TMR1CS = 0</u>

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RB6/T1OSO/T1CKI/PGC (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR1ON: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

**Note 1:** The oscillator inverter and feedback resistor are turned off to eliminate power drain.

####

### 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is Fosc/4. The synchronize control bit  $\overline{\text{T1SYNC}}$  (T1CON<2>) has no effect since the internal clock is always in sync.

### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the TMR1 register pair value increments on every rising edge of clock input on pin RB7/T1OSI/PGD when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI/PGC when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during Sleep mode, the TMR1 register pair value will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

## 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of the TMR1 register pair value after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to Table 17-8 in the Electrical Specifications Section, timing parameters 45, 46 and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4 Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications in Table 17-8, parameters 45, 46 and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

Note 1: When the T10SCEN bit is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

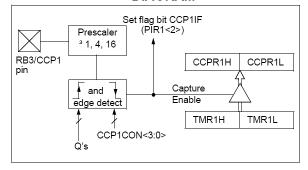

### 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit Capture register, as a 16-bit Compare register or as a PWM master/slave Duty Cycle register. Table 9-1 shows the timer resources of the CCP module modes.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the " $PIC^{\otimes}$  Mid-Range MCU Family Reference Manual" (DS33023).

### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### REGISTER 9-1: CCP1CON - CCP OPERATION REGISTER (ADDRESS: 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| _     | _   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 | •   | *     |       |        | •      | •      | bit 0  |

bit 7-6 **Unimplemented**: Read as '0'

bit 5-4 CCP1X:CCP1Y: PWM Least Significant bits

Capture Mode

Unused

Compare Mode Unused

PWM Mode

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCP1M<3:0>: CCPx Mode Select bits

0000 = Capture/Compare/PWM off (resets CCP1 module)

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, set output on match (CCP1IF bit is set)

1001 = Compare mode, clear output on match (CCP1IF bit is set)

1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)

1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1

11xx = PWM mode

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

An event is selected by control bits CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

**Note:** If the RB3/CCP1 is configured as an output, a write to the port can cause a capture condition.

## FIGURE 9-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

### 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M<3:0>. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

|       |             |                         |

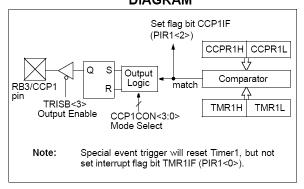

### 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- · Driven high

- · Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M<3:0> (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

## FIGURE 9-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 15.0 INSTRUCTION SET SUMMARY

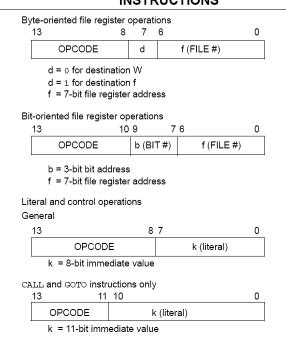

Each PIC16F627A/628A/648A instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F627A/628A/648A instruction set summary in Table 15-2 lists byte-oriented, bit-oriented, and literal and control operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

### 15.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "clrf PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                               |

| W     | Working register (accumulator)                                                                                                                                     |

| b     | Bit address within an 8-bit file register                                                                                                                          |

| k     | Literal field, constant data or label                                                                                                                              |

| X     | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| TO    | Time-out bit                                                                                                                                                       |

| PD    | Power-down bit                                                                                                                                                     |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 15-2 lists the instructions recognized by the MPASM $^{\mathsf{TM}}$  assembler.

Figure 15-1 shows the three general formats that the instructions can have.

- **Note 1:** Any unused opcode is reserved. Use of any reserved opcode may cause unexpected operation.

- 2: To maintain upward compatibility with future PIC MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where 'h' signifies a hexadecimal digit.

FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

TABLE 15-2: PIC16F627A/628A/648A INSTRUCTION SET

| Mnemonic,<br>Operands |      | Description                   | Cycles    |        | 14-Bit | Opcode | •    | Status   | Notes    |

|-----------------------|------|-------------------------------|-----------|--------|--------|--------|------|----------|----------|

|                       |      | Description                   |           | MSb    |        |        | LSb  | Affected | Notes    |

|                       |      | BYTE-ORIENTED FILE REGI       | STER OPER | RATION | IS     |        |      |          |          |

| ADDWF                 | f, d | Add W and f                   | 1         | 00     | 0111   | dfff   | ffff | C,DC,Z   | 1, 2     |

| ANDWF                 | f, d | AND W with f                  | 1         | 0.0    | 0101   | dfff   | ffff | Z        | 1, 2     |

| CLRF                  | f    | Clear f                       | 1         | 0.0    | 0001   | lfff   | ffff | Z        | 2        |

| CLRW                  | _    | Clear W                       | 1         | 0.0    | 0001   | 0xxx   | xxxx | Z        |          |

| COMF                  | f, d | Complement f                  | 1         | 0.0    | 1001   | dfff   | ffff | Z        | 1, 2     |

| DECF                  | f, d | Decrement f                   | 1         | 00     | 0011   | dfff   | ffff | Z        | 1, 2     |

| DECFSZ                | f, d | Decrement f, Skip if 0        | 1(2)      | 00     | 1011   | dfff   | ffff |          | 1, 2, 3  |

| INCF                  | f, d | Increment f                   | 1         | 00     | 1010   | dfff   | ffff | Z        | 1, 2     |

| INCFSZ                | f, d | Increment f, Skip if 0        | 1(2)      | 00     | 1111   | dfff   | ffff |          | 1, 2, 3  |

| IORWF                 | f, d | Inclusive OR W with f         | 1         | 00     | 0100   | dfff   | ffff | Z        | 1, 2     |

| MOVF                  | f, d | Move f                        | 1         | 00     | 1000   | dfff   | ffff | Z        | 1, 2     |

| MOVWF                 | f    | Move W to f                   | 1         | 00     | 0000   | lfff   | ffff |          |          |

| NOP                   | _    | No Operation                  | 1         | 00     | 0000   | 0xx0   | 0000 |          |          |

| RLF                   | f, d | Rotate Left f through Carry   | 1         | 00     | 1101   | dfff   | ffff | С        | 1, 2     |

| RRF                   | f, d | Rotate Right f through Carry  | 1         | 00     | 1100   | dfff   | ffff | С        | 1, 2     |

| SUBWF                 | f, d | Subtract W from f             | 1         | 00     | 0010   | dfff   | ffff | C,DC,Z   | 1, 2     |

| SWAPF                 | f, d | Swap nibbles in f             | 1         | 00     | 1110   | dfff   | ffff |          | 1, 2     |

| XORWF                 | f, d | Exclusive OR W with f         | 1         | 00     | 0110   | dfff   | ffff | Z        | 1, 2     |

|                       |      | BIT-ORIENTED FILE REGIS       | TER OPER  | ATIONS | 3      |        |      |          | <u> </u> |

| BCF                   | f, b | Bit Clear f                   | 1         | 01     | 00bb   | bfff   | ffff |          | 1, 2     |

| BSF                   | f, b | Bit Set f                     | 1         | 01     | 01bb   | bfff   | ffff |          | 1, 2     |

| BTFSC                 | f, b | Bit Test f, Skip if Clear     | 1(2)      | 01     | 10bb   | bfff   | ffff |          | 3        |

| BTFSS                 | f, b | Bit Test f, Skip if Set       | 1(2)      | 01     | 11bb   | bfff   | ffff |          | 3        |

|                       |      | LITERAL AND CONTRO            | OPERATION | ONS    |        |        |      |          |          |

| ADDLW                 | k    | Add literal and W             | 1         | 11     | 111x   | kkkk   | kkkk | C,DC,Z   |          |

| ANDLW                 | k    | AND literal with W            | 1         | 11     | 1001   | kkkk   | kkkk | Z        |          |

| CALL                  | k    | Call subroutine               | 2         | 10     | 0kkk   | kkkk   | kkkk | _        |          |

| CLRWDT                |      | Clear Watchdog Timer          | 1         | 00     | 0000   | 0110   | 0100 | TO,PD    |          |

| GOTO                  | k    | Go to address                 | 2         | 10     | 1kkk   | kkkk   | kkkk | . 0,1 2  |          |

| IORLW                 | k    | Inclusive OR literal with W   | 1         | 11     | 1000   | kkkk   | kkkk | z        |          |

| MOVLW                 | k    | Move literal to W             | 1         | 11     | 00xx   | kkkk   | kkkk | <u> </u> |          |

| RETFIE                | _    | Return from interrupt         | 2         | 00     | 0000   | 0000   | 1001 |          |          |

| RETLW                 | k    | Return with literal in W      | 2         | 11     | 01xx   | kkkk   | kkkk |          |          |

| RETURN                | _    | Return from Subroutine        | 2         | 00     | 0000   | 0000   | 1000 |          |          |

| SLEEP                 | _    | Go into Standby mode          | 1         | 00     | 0000   | 0110   | 0011 | TO,PD    |          |

| SUBLW                 | k    | Subtract W from literal       | i         | 11     | 110x   | kkkk   | kkkk | C,DC,Z   |          |

| XORLW                 | k    | Exclusive OR literal with W   | 1         | 11     | 1010   | kkkk   | kkkk | Z        |          |

| 22OICHW               | I.   | Exclusive Off literal with VV | 1         | 11     | 1010   | vvvv   | VVVV | _        |          |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### **ANNEXE C2**

### **Ultrasonic MA Series**

These sensors transmit and receive ultrasonic waves, having applications in distance measurement (vehicle reversing aids etc), object detecting, security alarms and remote control

#### Features

- 1. Compact and lightweight design

- 2. High sensitivity and sound pressure levels

- 3. Low power consumption

- 4. High reliability

- 5. Open, closed waterproof and high frequency options

#### Types

#### 1. Open Structure

Using the combined vibration mode of a bimorph transducer and radial core, this type exhibits high sensitivity and high sound pressure levels.

Applications: Automatic doors, Burglar Alarms, Remote control, Range finders.

#### 2. Water Proof

This type has excellent resistance to harsh environmental conditions and can be used outdoors. Applications: Back sonar of vehicles, Parking meters Water level meters.

### 3. High Frequency

Using longitudinal vibration and acoustic matching layer, this type exhibits high sensitivity in air.

Short wavelengths facilitate sharp directivity for high precision measurements.

Applications: Approach switches, distance measurements, liquid level meters, gas flow meters.

### 1- Open Structure Types

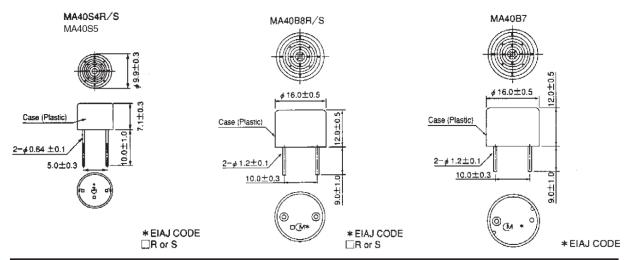

| Order Code      |       | MA4OS4R/S*    | MA40B8R/S*          | MA4OB7         | MA40S5      |  |  |  |

|-----------------|-------|---------------|---------------------|----------------|-------------|--|--|--|

| Construction    |       |               | Open structure type |                |             |  |  |  |

| Туре            |       | Sep. Receiver | & Transmitter       | Combined       | i type      |  |  |  |

| Norm. Freq.     | (kHz) |               |                     | 40             |             |  |  |  |