Ministère de l'enseignement supérieur et de la recherche scientifique Institut Supérieur des Etudes Technologiques de Sousse

Département Génie Electrique

Spécialité : Automatisme Informatique Industrielle – 2<sup>ème</sup> Année

Support de cours

# Microcontrôleur

# Ali HMIDENE

Agrégé en Génie Electrique

Technologue à l'ISET de Sousse

20010/2011

## TABLE DES MATIERES

| ŀ  | - 1  | NTRODUCTION AU MICROPROCESSEUR                 |

|----|------|------------------------------------------------|

| 1. | Stra | icture de base d'un calculateur                |

|    | our  |                                                |

| 2. | Arc  | hitecture d'un CPU                             |

|    | 2.1. | Unité arithmétique et logique                  |

|    | 2.2. | Les registres                                  |

|    | 2.3. | L'unité de contrôle (UC)                       |

| 3. | Fon  | ctionnement d'un microprocesseur               |

|    | 3.1. | Jeu instructions                               |

|    | 3.2. | Cycle d'exécution d'une instruction            |

|    | 3.3. | Les interruptions                              |

|    |      |                                                |

| 4. | Syst | ème à microprocesseur                          |

|    | 4.1. | Microprocesseur et Microcontrôleur             |

|    | 4.2. | Architecture des microprocesseurs              |

| II | - L  | LES MICROCONTROLEURS PIC16F876/8771            |

| 1. | Pré  | sentation                                      |

|    |      |                                                |

| 2. |      | actéristiques du PIC16F877                     |

|    | 2.1. | Caractéristique de la CPU                      |

|    | 2.2. | Caractéristiques des périphériques             |

|    | 2.3. | Brochage 1                                     |

| 3. | Arc  | hitecture interne du microcontrôleur PIC16F877 |

| 4. | Tra  | itement des Instructions                       |

| 5. | Org  | anisation de la mémoire1                       |

|    | 5.1. | Mémoire programme                              |

-1-

| 5.3. Registres Spéciaux (SFR)          | 16 |

|----------------------------------------|----|

| 6. Les Instructions                    | 18 |

| 6.1. Les modes d'adressage             | 19 |

| 7. Les Interruptions                   | 22 |

| III - LES PORTS D'ENTREE/SORTIE        | 25 |

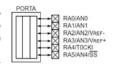

| 1. PORTA                               | 25 |

| 2. PORTB                               | 26 |

| 3. PORTC                               | 26 |

| 4. PORTD et PORTE                      | 26 |

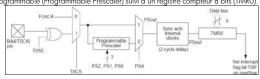

| IV - LES TIMERS                        | 29 |

| 1. Introduction                        | 29 |

| 2. Timer 0                             | 29 |

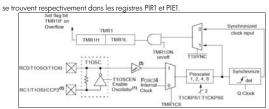

| 3. Timer 1                             | 31 |

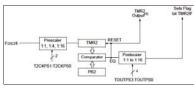

| 4. Timer 2                             | 32 |

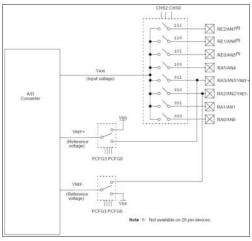

| V - CONVERTISSEUR ANALOGIQUE NUMERIQUE | 36 |

| 1. Présentation                        | 36 |

| 1.1. Registre ADCON1                   | 37 |

| 1.2. Registre ADCON0                   | 38 |

| 2. Conversion A/N                      | 39 |

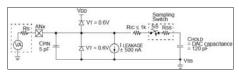

| 2.1. Temps d'acquisition               | 39 |

| 2.2. Temps de conversion               | 40 |

| 3. Etapes de programmation             | 41 |

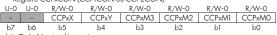

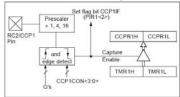

| VI - MODULE CAPTURE COMPARE PWM (CCP)  | 12 |

| 1.  | Prés | sentation                    | 42 |

|-----|------|------------------------------|----|

| 2.  | Mod  | tule CCP en mode capture     | 43 |

| 3.  | Mod  | lule CCP en mode Compare     | 43 |

| 4.  | Mod  | lule CCP en mode PWM         | 44 |

| VII | -    | L'INTERFACE SERIE            | 46 |

| 1.  | Prés | sentation                    | 46 |

| 2.  | Port | série du microcontrôleur PIC | 47 |

| 2   | 2.1. | Registre SPBRG               | 47 |

| 2   | 2.2. | Registre TXSTA               | 48 |

| 2   | 2.3. | Registre RCSTA               | 48 |

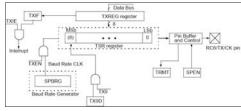

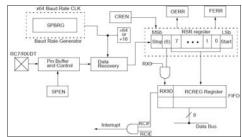

| 2   | 2.4. | Module d'émission            | 49 |

| 2   | 2.5  | Module de réception          | 50 |

# I - INTRODUCTION AU MICROPROCESSEUR

#### 1. Structure de base d'un calculateur

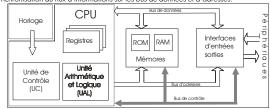

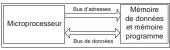

D'un point de vue matériel, un système informatique minimal est constitué d'un processeur, des mémoires et d'un ensemble des entrées sorties.

- Le microprocesseur (MPU, Micro-Processing Unit) est un circuit intégré à très grande échelle d'intégration (VLSI) capable d'exécuter automatiquement des instructions (opérations élémentaires) qu'il ira chercher dans la mémoire du micro-ordinateur. Il remplit donc les fonctions d'une unité centrale de traitement (CPU, Central Processing Unit) en un seul boîtier.

Toutes les informations qu'utilise le microprocesseur sont stockées dans des mémoires, en particulier le programme, le fonctionnement du microprocesseur est entièrement conditionné par le contenu de celles-ci. Ces mémoires contiennent deux types d'informations : le programme (ensemble des ordres à exécuter) et les données nécessaires pour la réalisation d'une tâche précise.

- Les données ou OPERANDES proviennent, le plus souvent, d'un calcul effectué par le microprocesseur ou d'un périphérique d'entrée, (clavier, disque, ...) via une interface. Elles sont stockées dans des mémoires qui peuvent être lues et écrites appelées RAM (Random Acces Memory).

- Les programmes figés sont placés, de façon définitive, dans des mémoires qui ne pourront qu'être lues par le microprocesseur. Ce sont des mémoires non volatiles, de type ROM (Read Only Memory), PROM, EPROM, Flash ...

- Dans un système à microprocesseur, l'interface d'entrée-sortie permet d'assurer la liaison entre l'unité centrale, via le bus interne du micro-ordinateur et l'environnement extérieur (périphériques).

Le microcontrôleur échange les informations avec les composants qui lui sont associés (mémoire et périphériques 1/O) au moyen d'un ensemble de connexions appelé bus. Un bus est un ensemble de fils qui assure la transmission du même type d'information. On retrouve trois types de bus véhiculant des informations en parallèle dans un système de traitement à microprocesseur :

- le bus de données : bidirectionnel qui assure le transfert des informations entre le microprocesseur et son environnement. Le nombre de lignes du bus de données définie la capacité de traitement du microprocesseur ; selon le microprocesseur la largeur du bus peut être de 8 bits, 16 bits, 32 bits, 64 bits ...

- le bus d'adresses: unidirectionnel qui permet la sélection de la case contenant l'information à traiter dans un *espace mémoire* (ou *espace adressable*). L'espace adressable peut avoir 2n emplacements, avec n est le nombre de lignes du bus d'adresses.

- le bus de commande: constitué par quelques conducteurs qui assurent la synchronisation du flux d'informations sur les bus de données et d'adresses.

Figure I-1 : Schéma bloc d'un système à microprocesseur

#### 2. Architecture d'un CPU

Le microprocesseur est constitué des unités fonctionnelles suivantes :

- d'unité Arithmétique et Logique (ALU),

- des registres,

- une unité de commande (CU).

#### 2.1. Unité arithmétique et logique

Cet organe, interne au microprocesseur, permet la réalisation d'opérations arithmétiques (Addition, Soustraction) et logiques (AND, OR, XOR...). Outre les opérations arithmétiques et logiques, l'ALU réalise aussi les opérations de décalage et de rotation. Le registre d'état est lié étroitement à L'ALU, nous donne à travers ces inducteurs (Flags) des renseignements supplémentaires sur le résultat d'une opération (résultat nul, négatif, dépassement...). On peut citer par exemple les indicateurs de :

- retenue (carry : C)

- retenue intermédiaire (Auxiliary-Carry : AC)

- signe (Sign : S)

- débordement (overflow : OV ou V)

- zéro (Z)

- parité (Parity : P)

- 5 -

#### 2.2. Les registres

Il existe deux types de registres : les registres d'usage général, et les registres d'adresses (pointeurs)

Les registres d'usage général (Registre de travail)

Ce sont des mémoires rapides, à l'intérieur du microprocesseur, qui permettent à l'UAL de manipuler des données à vitesse élevée. Ils sont connectés au bus de données interne du microprocesseur.

L'adresse d'un registre est associée à son nom (on donne généralement comme nom une lettre A, B, C...). L'accumulateur est un registre de travail qui sert à stocker un opérande au début d'une opération et/ou le résultat à la fin de l'opération.

Les registres d'adresses (pointeurs)

Ce sont des registres connectés sur le bus adresses.

On peut citer comme registre:

- Le compteur ordinal (pointeur de programme PC): celui-ci contient toujours l'adresse de la prochaine instruction à exécuter.

- Le pointeur de pile (Stack Pointer SP), utilisé pour la sauvegarde de l'adresse de retour d'un sous-programme.

- Les registres pointeur de données ou d'index : utilisés pour l'adressage indirect de la mémoire.

# 2.3. L'unité de contrôle (UC)

Elle permet de séquencer le déroulement des instructions. Elle effectue la recherche en mémoire des instructions, décodage et exécuté l'instruction recherchée. Elle est composée essentiellement :

- d'un *registre d'instruction* (RI), recevant le code de l'instruction à exécuter

- d'un *décodeur d'instruction*, permettant de déterminer le type de l'instruction à exécuter.

- d'un *Bloc logique de commande (ou séquenceur)* : Il organise l'exécution des instructions au rythme d'une horloge, et élabore tous les signaux de synchronisation internes ou externes du microprocesseur.

# 3. Fonctionnement d'un microprocesseur

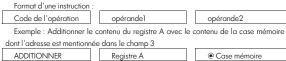

# 3.1. Jeu Instructions

Les microprocesseurs sont capables d'effectuer un certain nombre d'opérations élémentaires. Cet ensemble d'opérations élémentaires est appelé jeu d'instructions. Une instruction au niveau machine doit fournir à l'unité centrale toutes les informations nécessaires pour déclencher une telle opération élémentaire. Elle comporte en général plusieurs champs ; le premier champ contient le code de l'opération (*Code-Op* ou *Op-Code* en anglais); les autres champs peuvent comporter des données ou l'identification des opérandes. Sur certaines machines les instructions ont toutes la même longueur, sur d'autres cette longueur peut varier avec le code opération ou le mode d'adressage.

# 3.2. Cycle d'exécution d'une instruction

Le traitement d'une instruction peut être décomposé en plusieurs phases. Celles-ci sont au nombre de trois :

- ✓ Recherche de l'instruction (Fetch)

- ✓ Décodage (decode)

- ✓ Exécution (execute)

# 3.2.1. Recherche d'une instruction (Fetch)

Le contenu de PC (compteur ordinal) est placé sur le bus des adresses (c'est l'unité de contrôle qui établit la connexion). L'unité de contrôle (UC) émet un ordre de lecture (READ=RD=1), au bout d'un certain temps (temps d'accès à la mémoire) le contenu de la case mémoire sélectionné est disponible sur le bus des données.L'unité de contrôle charge la donnée dans le registre d'instruction pour décodage.

Figure I-2 : Recherche de l'instruction

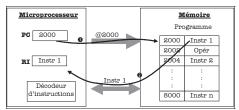

#### 3.2.2. Décodage

Le registre d'instruction (RI) contient maintenant le premier mot de l'instruction qui peut être codée sur plusieurs mots. Ce premier mot contient le <u>code opératoire</u> qui définit la nature de l'opération à effectuer (addition, rotation,...) et le nombre de mots de l'instruction. L'unité de commande décode le code opératoire. Si l'instruction est suivie d'un opérande (une constante ou adresse d'une donnée), l'unité de contrôle

cupère cet opérande, et positionne le compteur ordinal (PC) sur l'instruction suivant Microprocesseur 0 Mémoire Programme Logique de 2004 2000 Instr 1 commande 2002 Opér Instr 2 RI Instr 1 Opér Décodeur d'instruction 8000 Instr n Tmp Opér

Figure I-3 : Récupération de l'opérande

#### 3.2.3. Exécution

Le microprogramme réalisant l'instruction est exécuté. Les indicateurs sont positionnés (registre d'état).

L'exemple suivante montre l'exécution d'une addition d'un Opérande se trouvant dans un registre temporaire (Tmp) avec le contenu du registre A, le résultat est chargé dans le registre A.

Figure I-4 : Exécution de l'instruction

- 8 -

- l'architecture Harvard, sépare systématiquement la mémoire de programme de la

d'architecture est utilisé sur des microcontrôleurs qui ont connu un développement important ces dernières années.

L'architecture généralement utilisée par les microprocesseurs est la structure Von Neuman (exemples : la famille Motorola 68XXX, la famille Intel 80x86). L'architecture Harvard est plutôt utilisée dans des microprocesseurs spécialisés pour des applications temps réels, tel que les DSP, les microcontrôleurs PIC, les AVR...

mémoire des données : l'adressage de ces mémoires est indépendant. Ce type

Figure I-5 : Architecture Von Neuman

Figure I-6 : Architecture Harvard

#### 3.3. Les Interruptions

Le microprocesseur exécute les instructions de manière séquentielle. Souvent, il est nécessaire d'interrompre un programme pour exécuter une tâche supposée prioritaire. Cette tâche (appelée routine d'interruption) est déclenchée suite à un évènement extérieur.

Une fois que l'interruption à été servie (exécutée) le programme principal reprend son exécution à partir de l'endroit où il a été interrompu.

Le microprocesseur possède des broches spécialisées pour les interruptions. Si un composant extérieur au microprocesseur veut l'interrompre, il lui suffit de changer l'état d'une de ces broches (0  $\Rightarrow$ 1 ou  $1\Rightarrow$ 0 suivant l'état les broches). Le sous-programme d'interruption est placé en mémoire par le concepteur à une adresse connue par microprocesseur.

#### 4. Système à microprocesseur

#### 4.1. Microprocesseur et Microcontrôleur

Au début de la commercialisation des microprocesseurs, un système minimum était obligatoirement constitué de plusieurs circuits intégrés.

Les microcontrôleurs sont apparus ensuite, lorsque l'intégration des composants a fait des progrès considérables. Actuellement, dans un circuit intégré, un microcontrôleur regroupe l'équivalent d'un système à microprocesseur dans un même boîtier. Un système à microprocesseur peut être constitué de nombreux composants (mémoires, etc.); il est facilement extensible. Les constituants d'un microcontrôleur sont figés.

Les microcontrôleurs sont plutôt dédiés aux applications qui ne nécessitent pas une grande quantité de calculs complexes, mais qui demandent beaucoup de manipulations d'entrées/sorties. C'est le cas de contrôle de processus.

Les systèmes à microprocesseur sont plutôt réservés pour les applications demandant beaucoup de traitement de l'information et assez peu de gestion d'entrées / sorties. Les ordinateurs sont réalisés avec des systèmes à microprocesseur.

#### 4.2. Architecture des microprocesseurs

Pour l'organisation des différentes unités, il existe deux architectures :

- l'architecture Von Neuman (du nom d'un des savants qui a contribué à la mise au point d'un des tout premiers ordinateurs). La mémoire programme, la mémoire données et les périphériques d'entrées/sorties partagent le même bus s'adresses et de données.

- 9 -

# II - LES MICROCONTROLEURS PIC16F876/877

# 1. Présentation

Les microcontrôleurs PICs sont des composants dits RISC (Reduce Instructions Set Computing), ou encore composants à jeu d'instructions réduit. Tous les PICs Mid-Range ont un jeu de 35 instructions, stockent chaque instruction dans un seul mot de programme, et exécutent chaque instruction (sauf les sauts) en un cycle machine. On atteint donc des très grandes vitesses.

L'horloge fournie au PIC est divisée par 4. C'est cette base de temps qui donne le temps d'un cycle. Si on utilise par exemple un quartz de 4MHz, on obtient donc 1000000 de cycles/seconde; or, comme le PIC exécute pratiquement une instruction par cycle, hormis les sauts, cela nous donne une puissance de l'ordre de 1MIPS (1 Million d'Instructions Par Seconde).

- Les microcontrôleurs PICs sont subdivisés en 3 grandes familles :

- La famille Base-Line, utilise des mots d'instructions de 12 bits,

- la famille Mid-Range, utilise des mots de 14 bits « PIC16 »,

- la famille High-End, utilise des mots de 16 bits. « PIC17 et PIC18 »

Nous allons dans ce document étudier le microcontrôleur PIC16F877, qui n'est rien d'autre qu'un PIC16F84 amélioré.

# 2. Caractéristiques du PIC16F877

# 2.1. Caractéristique de la CPU

- ⇒ CPU à architecture RISC (8 bits)

- ⇒ Mémoire programme de 8 Kmots de 14 bits (Flash),

- ⇒ Mémoire donnée de 368 Octets,

- ⇒ EEPROM donnée de 256 Octets,

- ⇒ 14 sources d'interruptions,

- $\Rightarrow$  5 ports d'entrées/sorties bidirectionnels,

- ⇒ Pile de 8 niveaux,

- ⇒ Oscillateurs de type RC ou Quartz (Fmax = 20MHz),

- ho Programmation en mode série de la mémoire Flash à travers les broches RB6/PGC et RB7/PGD,

- ⇔ Chien de garde (WatchDog),

# 2.2. Caractéristiques des périphériques

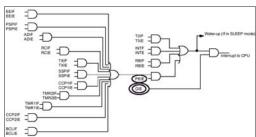

- ⇒ Timer0 : Timer/Compteur 8 bits avec un prédiviseur 8 bits

- $\Rightarrow$  Timer1 : Timer/Compteur 16 bits avec un prédivision de 1, 2, 4, ou 8 ; il peut être incrémenté en mode veille (Sleep), via une horloge externe,

- ⇒ Timer2 : Timer 8 bits avec deux diviseurs (pré et post diviseur)

- Deux modules « Capture, Compare et PWM »

- → Module capture 16 bits avec une résolution max. 12,5 ns.

- ⇔ Module Compare 16 bits avec une résolution max. 200 ns,

- ➡ Module PWM avec une résolution max. 10 bits,

- ⇒ ADC multi-canal (8 voies) avec une conversion sur 10 bits,

- ⇒ Synchronous Serial Port (SSP) travaillant en mode SPI et en mode 12C (mode

- $\Rightarrow$  Universel Synchronous Asynchronous Receiver Transmitter (USART/SCI) avec un 9<sup>ème</sup> bit pour la détection d'adresse.

- ⇒ Parallel Slave Port de 8 bits avec signaux de contrôle externes RD\, RW\ et CS\.

#### 2.3. Brochage

Figure II-1 : Brochages des microcontrôleurs PIC

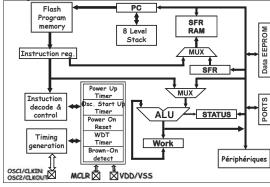

#### Architecture interne du microcontrôleur PIC16F877

Les microcontrôleurs la famille PIC16 se base sur une architecture RISC, cette architecture permet une accessibilité séparée de la mémoire programme et celle des données avec un nombre d'instructions très réduit (35 insts.). Le compteur de programme des microcontrôleurs Mid-range est de 13 bits : ils peuvent donc adresser 8Kmots au maximum.

La pile du PIC est constituée d'une mémoire circulaire (LIFO) de 8 niveaux, par conséquent, il n'est pas possible de faire plus de 8 empilements successifs ; de plus elle n'est pas accessible à l'utilisateur.

La Figure II-2, montre la structure interne des microcontrôleurs PIC16.

Figure II-2 : Architecture interne

#### 4. Traitement des instructions

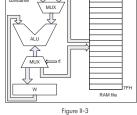

L'UAL reçoit les arguments (opérandes) de l'unique registre de travail (Work) et la mémoire de données (File). Le résultat de traitement pourra être stocké, selon la valeur du bit d, dans registre W (d = 0) ou dans le mémoire File (d = 1). Il est a noté que le mémoire File comprend les registres du CPU (STATUS, FSR, PCLATH, PCL), les registres des périphériques I/O et la mémoire de données utilisateur.

Avec cette structure le microcontrôleur PIC utilise trois modes d'adressage :

- 13 -

- 12 -

- *Adressage immédiat (Litéral)*: ce mode ne fait pas intervenir le mémoire de données (File). Exemple : ADDLW Const ;  $W \leftarrow W + Const$ .

- Adressage direct : Ce mode fait intervenir l'accumulateur W et la mémoire File. Le résultat pourra être chargé selon la valeur du bit d, dans W ou File. Exemple : ADDWF F,d

Si d = 0, alors  $W \leftarrow W + (F)$

Si d = 1, alors (F)  $\leftarrow$  W + (F)

Adressage indirect utilisant le registre FSR pour pointer la donnée.

# 5. Organisation de la mémoire

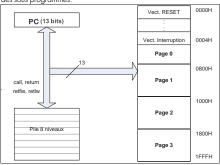

# 5.1. Mémoire programme

La mémoire programme est constituée de 8 Kmots de 14 bits. Le vecteur Reset occupe l'adresse 0000H, alors que le vecteur d'interruption occupe l'adresse 0004H. La mémoire programme est divisée en 4 pages (2 Kmots par page).

Microchip a réservé une zone de pile de 8 niveaux pour l'empilement des adresses de retour des sous programmes.

Figure II-4 : Adressage de la mémoire programme

# 5.2. Mémoire données

La mémoire de données (File Registers) compte au total 512 octets, reparties sur 4 banques (0, 1, 2 et 3); dans chacune des banques vous trouvez des cases mémoires spéciales appelées «SPECIAL FUNCTION REGISTRES (SFR) », et des cases mémoires à usage général appelées GENERAL PURPOSE REGISTER (GPR).

La zone des registres SFR comporte les registres du CPU et celles des périphériques.

La partie restante GPR, constitue la mémoire de stockage des données utilisateur. Dans le cas des PIC16F876/877, elle compte au total 368 octets, reparties de la manière suivante

96 octets (80 octets dans la banque 0 et 16 Octets zone commune)

80 octets dans la banque 1,

96 octets dans la banque 2 96 octets dans la banque 3.

L'accès à la zone commune n'impose pas la sélection de la banque

| Indirect addr.(1)                          | 00h | Indirect addr.(1)                          | 80h | Indirect addr.(*)                          | 100h | Indirect addr.(*)                          | 180h |

|--------------------------------------------|-----|--------------------------------------------|-----|--------------------------------------------|------|--------------------------------------------|------|

| TMR0                                       | 01h | OPTION_REG                                 | 81h | TMR0                                       | 101h | OPTION_REG                                 | 181h |

| PCL                                        | 02h | PCL                                        | 82h | PCL                                        | 102h | PCL                                        | 182h |

| STATUS                                     | 03h | STATUS                                     | 83h | STATUS                                     | 103h | STATUS                                     | 183h |

| FSR                                        | 04h | FSR                                        | 84h | FSR                                        | 104h | FSR                                        | 184h |

| PORTA                                      | 05h | TRISA                                      | 85h |                                            | 105h |                                            | 185h |

| PORTB                                      | 06h | TRISB                                      | 86h | PORTB                                      | 106h | TRISB                                      | 186h |

| PORTC                                      | 07h | TRISC                                      | 87h |                                            | 107h |                                            | 187h |

| PORTD (1)                                  | 08h | TRISD (1)                                  | 88h | 8 3                                        | 108h |                                            | 188h |

| PORTE (1)                                  | 09h | TRISE(1)                                   | 89h |                                            | 109h |                                            | 189h |

| PCLATH                                     | 0Ah | PCLATH                                     | 8Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah |

| INTCON                                     | 0Bh | INTCON                                     | 8Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh |

| PIR1                                       | 0Ch | PIE1                                       | 8Ch | EEDATA                                     | 10Ch | EECON1                                     | 18CH |

| PIR2                                       | 0Dh | PIE2                                       | 8Dh | EEADR                                      | 10Dh | EECON2                                     | 18Dh |

| TMR1L                                      | 0Eh | PCON                                       | 8Eh | EEDATH                                     | 10Eh | Reserved <sup>(2)</sup>                    | 18EH |

| TMR1H                                      | 0Fh |                                            | 8Fh | EEADRH                                     | 10Fh | Reserved <sup>(2)</sup>                    | 18Fh |

| T1CON                                      | 10h |                                            | 90h |                                            | 110h |                                            | 190h |

| TMR2                                       | 11h | SSPCON2                                    | 91h |                                            | 111h |                                            | 191h |

| T2CON                                      | 12h | PR2                                        | 92h |                                            | 112h |                                            | 192h |

| SSPBUF                                     | 13h | SSPADD                                     | 93h |                                            | 113h |                                            | 193h |

| SSPCON                                     | 14h | SSPSTAT                                    | 94h |                                            | 114h |                                            | 194h |

| CCPR1L                                     | 15h | ***************************************    | 95h |                                            | 115h |                                            | 195h |

| CCPR1H                                     | 16h |                                            | 96h | 00/05/2005                                 | 116h | 10.000000000                               | 196h |

| CCP1CON                                    | 17h |                                            | 97h | General                                    | 117h | General<br>Purpose                         | 197h |

| RCSTA                                      | 18h | TXSTA                                      | 98h | Purpose<br>Register                        | 118h | Register                                   | 198h |

| TXREG                                      | 19h | SPBRG                                      | 99h | 16 Bytes                                   | 119h | 16 Bytes                                   | 199h |

| RCREG                                      | 1Ah |                                            | 9Ah |                                            | 11Ah |                                            | 19A  |

| CCPR2L                                     | 1Bh |                                            | 9Bh |                                            | 11Bh |                                            | 19Bh |

| CCPR2H                                     | 1Ch |                                            | 9Ch |                                            | 11Ch |                                            | 1901 |

| CCP2CON                                    | 1Dh |                                            | 9Dh |                                            | 11Dh |                                            | 19DH |

| ADRESH                                     | 1Eh | ADRESL                                     | 9Eh |                                            | 11Eh |                                            | 19Eh |

| ADCON0                                     | 1Fh | ADCON1                                     | 9Fh |                                            | 11Fh |                                            | 19Fh |

|                                            | 20h |                                            | A0h |                                            | 120h |                                            | 1A0h |

| General<br>Purpose<br>Register<br>96 Bytes |     | General<br>Purpose<br>Register<br>80 Bytes | EFh | General<br>Purpose<br>Register<br>80 Bytes | 16Fh | General<br>Purpose<br>Register<br>80 Bytes | 1EFI |

|                                            | 75. | accesses<br>70h-7Fh                        | F0h | accesses<br>70h-7Fh                        | 170h | accesses<br>70h - 7Fh                      | 1F0h |

| Bank 0                                     | 7Fh | Bank 1                                     | FFh | Bank 2                                     | 1778 | Bank 3                                     | irre |

Figure II-5 : Mémoire de données

Deux modes d'adressage sont utilisés pour l'accès à la mémoire File

- adressage direct : les 7 bits (b<sub>6</sub> .. b<sub>0</sub>) de la partie basse de l'adresse font partie du code de l'instruction ; la partie haute de l'adresse est constituée des bits RP1 et RPO du registre STATUS.

Dans ce mode d'adressage, tout accès à la mémoire est précédé par la sélection d'une banque selon le tableau suivant :

| RP1 : RPO | Banque   | Zone d'adressage |

|-----------|----------|------------------|

| 0.0       | Banque O | 00H 7FH          |

| 01        | Banque 1 | 80H FFH          |

| 10        | Banque 2 | 100H 17FH        |

| 11        | Banque 3 | 180H 1FFH        |

- adressage indirect : la partie basse de l'adresse est fournie par le registre FSR (File Select Register). La sélection d'une banque est réalisée dans ce cas par le 8 bits du registre FSR et le bit IRP du registre STATUS.

Figure II-6 : Adressage de la RAM file

#### 5.3. Registres Spéciaux (SFR)

Les SFR « Special Function Registers » sont implémentés en RAM statique (File) et occupent les parties basses des banques. Ces registres sont classés en deux catégories ; certains liés au CPU et les autres pour le contrôle des périphériques. Nous allons décrire dans cette partie les registres attachés au CPU.

#### 5.3.1. Le registre STATUS

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RPO   | TO\ | PD\ | DC    | Z     | С     |

| b7    | b6    | b5    | b4  | b3  | b2    | b1    | b0    |

- 16 -

Bit 7 : IRP : sélection des banques en adressage indirect.

IRP = 0 : banque 0, 1

IRP = 1: banque 2, 3

Bits 6 et 5: RP1 et RPO: sélection des banques en adressage direct

Bit 4: TO\: Time Out bit (bit en lecture seulement).

TO\ = 1 : Après une mise sous tension, après l'instruction CLRWDT ou bien après l'instruction SLEEP.

TO = 0: Signifie qu'un Time Out du timer de watchdog est survenu

Bit 3: PD\ = Power Down bit (bit en lecture seulement)

PD\ = 1 : Après une mise sous tension ou bien après une RAZ du Watchdog.

PD\ = 0 : Après l'instruction SLEEP.

Bit 2: Z = Zero bit.

Z = 1 : Le résultat d'une opération arithmétique ou logique est nul.

Z = 0 : Le résultat d'une opération arithmétique ou logique est différent de

zéro. Ce bit est positionné aussi par l'instruction « movf »

Bit 1: DC = Digit Carry/ borrow bit (affecté par ADDWF, ADDLW, SUBWF et SUBLW). Ce bit est inversé en cas d'un emprunt.

DC = 1 : Une retenue sur le 4<sup>ème</sup> bit des poids faible est survenue.

DC = 0 : Pas de retenue sur le 4<sup>ème</sup> bit des poids faible.

Bit O : C = Carry/ $\overline{borrow}$  bit (affecté par ADDWF, ADDLW, SUBWF et SUBLW). Ce bit est inversé en cas d'un emprunt. C = 1 : Une retenue sur le bit MSB est survenue.

C = 0 : Pas de retenue sur le bit MSB.

# 5.3.2. Le registre PCON

| U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-----|-----|-----|-----|-----|-----|-------|-------|

|     |     |     |     |     |     | POR\  | BOR\  |

| b7  | b6  | b5  | b4  | b3  | b2  | b1    | Ь0    |

$\mathit{Bit 1}$ : POR\: Power-on Reset Status bit.

POR = 1: Pas de Power-on Reset.

$POR \ = 0$ : Power-on Reset est survenue (ce bit doit être mis à 1 après un POR).

Bit O · BOR\ · Brown-out Reset Status bit

BOR = 1: Pas de Brown-out Reset Une.

BOR\ = 0 : Brown-out Reset est survenue (ce bit doit être mis à 1 après un BOR).

Associés au bit TO\ du registre STATUS, ces permettent de déterminer la source de RESET

- 17 -

5.3.3. Le Compteur de Programme (PC: PCLATH et PCL)

Le compteur de programme PC a une largeur de 13 bits (8Kmots). La partie basse de l'adresse se trouve dans le registre PCL, alors que la partie haute (b<sub>12</sub> .. b<sub>8</sub>) se trouve dans le registre PCH. Ce dernier n'est pas accessible, mais il peut être modifié indirectement à travers le registre PCLATH.

Deux cas possibles permettent de modifier le contenu du registre PC :

- Instruction de saut calculé en cours d'exécution du programme ; cette instruction permet de parcourir un tableau constant en ajoutant à PCL le contenu du registre W. Dans ce cas le contenu de PCLATH est chargé automatiquement dans PCH.

- Instructions de branchement (call et goto). Le 11 bits d'adresse sont fournit par l'instruction de branchement. Le deux bits restants ( $b_{12}$  et  $b_{11}$ ) seront chargé depuis le reaistre PCLATH

Figure II-7: Registre PCLATH

# Les Instructions

La famille Mid-Range, possède 35 instructions codées sur des mots de 14 bits. Ces instructions comportent le code opératoire « OPCODE » pour spécifier le type de l'instruction et un ou deux opérandes. Microchip a regroupée ses instructions en trois catégories (voir Figure II-8) :

- les instructions orientée octet (byte),

- les instructions orientée bit,

- les instructions à adressage immédiat et de contrôle.

| Mnemoric,<br>Operands |      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Cycles         | 14-B    | t Opcod  | Status | Notes |          |       |

|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|----------|--------|-------|----------|-------|

|                       |      | The second secon |                | MSb LSb |          |        |       | Affected |       |

|                       |      | BYTE-ORIENTED FIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E REGISTER OPE | RATIO   | )NS      |        |       |          |       |

| ADDWF                 | f, d | Add W and f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1              | 00      | 0111     | dree   | tttt  | C,DC,Z   | 1,2   |

| ANDWF                 | f, d | AND W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1              | 0.0     | 0101     | dfff   | tttt  | Z        | 1,2   |

| CLRF                  | 1    | Clear f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - 3            | 0.0     | 0001     | lfff   | tttt  | - 2      | 2     |

| CLRW                  |      | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1              | 0.0     | 0001     | OXXX   | XXXX  | Z        |       |

| COMF                  | f, d | Complement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 1            | 00      | 1001     | dfff   | tttt  | Z        | 1,2   |

| DECF                  | f, d | Decrement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.1            | 00      | 0011     | dfff   | tttt  | Z        | 1,2   |

| DECFSZ                | f, d | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1(2)           | 0.0     | 1011     | dfff   | tttt  |          | 1,2,3 |

| INCF                  | f, d | Increment f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1              | 0.0     | 1010     | dfff   | tttt  | Z        | 1,2   |

| INCFSZ                | f, d | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1(2)           | 00      | 1111     | dfff   | tttt  |          | 1,2,3 |

| IORWF                 | f, d | Inclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1              | 0.0     | 0100     | dfff   | tttt  | Z        | 1.2   |

| MOVE                  | f, d | Move f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1             | 0.0     | 1000     | dree   | tttt  | Z        | 1,2   |

| MOVWE                 | 1    | Move W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 1            | 00      | 0000     | 1555   | ffff  |          |       |

| NOP                   |      | No Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1              | 00      | 0000     | 03000  | 0000  |          |       |

| RLF                   | f.d  | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | 00      | 1161     | dees   | tttt  | C        | 1.2   |

| RRF                   | f, d | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.1            | 00      | 1100     | dfff   | tttt  | . C      | 1,2   |

| SUBWE                 | f, d | Subtract W from f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 00      | 0010     | dfff   | tttt  | CDCZ     | 1.2   |

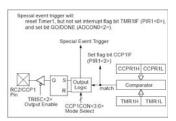

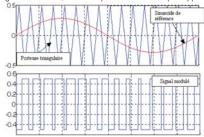

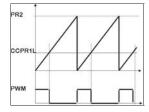

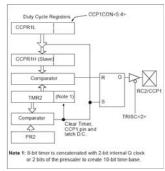

| SWAPF                 | f, d | Swap nibbles in f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | 00      | 1110     | dree   | 1111  |          | 1.2   |