# 13.13 ADC registers

Refer to Section 1.1 on page 57 for a list of abbreviations used in register descriptions.

The peripheral registers must be written at word level (32 bits). Read accesses can be done by bytes (8 bits), half-words (16 bits) or words (32 bits).

# 13.13.1 ADC status register (ADC\_SR)

Address offset: 0x00

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27  | 26     | 25 | 24  | 23     | 22 | 21    | 20    | 19    | 18    | 17    | 16    |

|----|----|----|----|-----|--------|----|-----|--------|----|-------|-------|-------|-------|-------|-------|

|    |    |    |    |     |        |    | Res | served |    |       |       |       |       |       |       |

| 15 | 14 | 13 | 12 | 11  | 10     | 9  | 8   | 7      | 6  | 5     | 4     | 3     | 2     | 1     | 0     |

|    |    |    |    | Doo | served |    |     |        |    | OVR   | STRT  | JSTRT | JEOC  | EOC   | AWD   |

|    |    |    |    | Res | serveu |    |     |        |    | rc_w0 | rc_w0 | rc_w0 | rc_w0 | rc_w0 | rc_w0 |

Bits 31:6 Reserved, must be kept at reset value.

#### Bit 5 OVR: Overrun

This bit is set by hardware when data are lost (either in single mode or in dual/triple mode). It is cleared by software. Overrun detection is enabled only when DMA = 1 or EOCS = 1.

- 0: No overrun occurred

- 1: Overrun has occurred

#### Bit 4 STRT: Regular channel start flag

This bit is set by hardware when regular channel conversion starts. It is cleared by software.

- 0: No regular channel conversion started

- 1: Regular channel conversion has started

## Bit 3 JSTRT: Injected channel start flag

This bit is set by hardware when injected group conversion starts. It is cleared by software.

- 0: No injected group conversion started

- 1: Injected group conversion has started

#### Bit 2 **JEOC**: Injected channel end of conversion

This bit is set by hardware at the end of the conversion of all injected channels in the group. It is cleared by software.

- 0: Conversion is not complete

- 1: Conversion complete

## Bit 1 EOC: Regular channel end of conversion

This bit is set by hardware at the end of the conversion of a regular group of channels. It is cleared by software or by reading the ADC\_DR register.

- 0: Conversion not complete (EOCS=0), or sequence of conversions not complete (EOCS=1)

- 1: Conversion complete (EOCS=0), or sequence of conversions complete (EOCS=1)

## Bit 0 AWD: Analog watchdog flag

This bit is set by hardware when the converted voltage crosses the values programmed in the ADC\_LTR and ADC\_HTR registers. It is cleared by software.

- 0: No analog watchdog event occurred

- 1: Analog watchdog event occurred

#### 13.13.2 ADC control register 1 (ADC\_CR1)

Address offset: 0x04

Reset value: 0x0000 0000

| 31  | 30     | 29      | 28          | 27         | 26    | 25         | 24   | 23     | 22     | 21    | 20 19 18 17 1 |      |       |   |    |

|-----|--------|---------|-------------|------------|-------|------------|------|--------|--------|-------|---------------|------|-------|---|----|

|     |        | Reserve | od          |            | OVRIE | RE         | S    | AWDEN  | JAWDEN |       |               | Rese | n rod |   |    |

|     |        | Reserv  | eu          |            | rw    | rw         | rw   | rw     | rw     |       |               | Rese | erveu |   |    |

| 15  | 14     | 13      | 12          | 11         | 10    | 9          | 8    | 7      | 6      | 5     | 4             | 3    | 2     | 1 | 0  |

| DIS | SCNUM[ | 2:0]    | JDISCE<br>N | DISC<br>EN | JAUTO | AWDSG<br>L | SCAN | JEOCIE | AWDIE  | EOCIE | E AWDCH[4:0]  |      |       |   |    |

| rw  | rw     | rw      | rw          | rw         | rw    | rw         | rw   | rw     | rw     | rw    | rw rw rw r    |      |       |   | rw |

Bits 31:27 Reserved, must be kept at reset value.

Bit 26 **OVRIE:** Overrun interrupt enable

This bit is set and cleared by software to enable/disable the Overrun interrupt.

0: Overrun interrupt disabled

1: Overrun interrupt enabled. An interrupt is generated when the OVR bit is set.

### Bits 25:24 RES[1:0]: Resolution

These bits are written by software to select the resolution of the conversion.

00: 12-bit (15 ADCCLK cycles) 01: 10-bit (13 ADCCLK cycles) 10: 8-bit (11 ADCCLK cycles) 11: 6-bit (9 ADCCLK cycles)

Bit 23 AWDEN: Analog watchdog enable on regular channels

This bit is set and cleared by software.

0: Analog watchdog disabled on regular channels

1: Analog watchdog enabled on regular channels

## Bit 22 JAWDEN: Analog watchdog enable on injected channels

This bit is set and cleared by software.

0: Analog watchdog disabled on injected channels

1: Analog watchdog enabled on injected channels

Bits 21:16 Reserved, must be kept at reset value.

### Bits 15:13 DISCNUM[2:0]: Discontinuous mode channel count

These bits are written by software to define the number of regular channels to be converted in discontinuous mode, after receiving an external trigger.

000: 1 channel 001: 2 channels

111: 8 channels

## Bit 12 JDISCEN: Discontinuous mode on injected channels

This bit is set and cleared by software to enable/disable discontinuous mode on the injected channels of a group.

0: Discontinuous mode on injected channels disabled

1: Discontinuous mode on injected channels enabled

416/1718 DocID018909 Rev 8

### Bit 11 DISCEN: Discontinuous mode on regular channels

This bit is set and cleared by software to enable/disable Discontinuous mode on regular channels.

- 0: Discontinuous mode on regular channels disabled

- 1: Discontinuous mode on regular channels enabled

#### Bit 10 JAUTO: Automatic injected group conversion

This bit is set and cleared by software to enable/disable automatic injected group conversion after regular group conversion.

- 0: Automatic injected group conversion disabled

- 1: Automatic injected group conversion enabled

## Bit 9 AWDSGL: Enable the watchdog on a single channel in scan mode

This bit is set and cleared by software to enable/disable the analog watchdog on the channel identified by the AWDCH[4:0] bits.

- 0: Analog watchdog enabled on all channels

- 1: Analog watchdog enabled on a single channel

## Bit 8 SCAN: Scan mode

This bit is set and cleared by software to enable/disable the Scan mode. In Scan mode, the inputs selected through the ADC SQRx or ADC JSQRx registers are converted.

- 0: Scan mode disabled

- 1: Scan mode enabled

Note: An EOC interrupt is generated if the EOCIE bit is set:

- At the end of each regular group sequence if the EOCS bit is cleared to 0

- At the end of each regular channel conversion if the EOCS bit is set to 1

Note: A JEOC interrupt is generated only on the end of conversion of the last channel if the JEOCIE bit is set.

## Bit 7 **JEOCIE**: Interrupt enable for injected channels

This bit is set and cleared by software to enable/disable the end of conversion interrupt for injected channels.

- 0: JEOC interrupt disabled

- 1: JEOC interrupt enabled. An interrupt is generated when the JEOC bit is set.

## Bit 6 AWDIE: Analog watchdog interrupt enable

This bit is set and cleared by software to enable/disable the analog watchdog interrupt.

- 0: Analog watchdog interrupt disabled

- 1: Analog watchdog interrupt enabled

#### Bit 5 EOCIE: Interrupt enable for EOC

This bit is set and cleared by software to enable/disable the end of conversion interrupt.

- 0: EOC interrupt disabled

- 1: EOC interrupt enabled. An interrupt is generated when the EOC bit is set.

## Bits 4:0 AWDCH[4:0]: Analog watchdog channel select bits

These bits are set and cleared by software. They select the input channel to be guarded by the analog watchdog.

Note: 00000: ADC analog input Channel0 00001: ADC analog input Channel1

...

01111: ADC analog input Channel15 10000: ADC analog input Channel16 10001: ADC analog input Channel17 10010: ADC analog input Channel18

Other values reserved

# 13.13.3 ADC control register 2 (ADC\_CR2)

Address offset: 0x08

Reset value: 0x0000 0000

| 31       | 30          | 29  | 28  | 27    | 26   | 25      | 24  | 23       | 22           | 21     | 20   | 19 | 18    | 17      | 16   |

|----------|-------------|-----|-----|-------|------|---------|-----|----------|--------------|--------|------|----|-------|---------|------|

| reserved | SWST<br>ART | EXT | ΓΕΝ |       | EXTS | EL[3:0] |     | reserved | JSWST<br>ART | JEXT   | EN   |    | JEXTS | EL[3:0] |      |

|          | rw          | rw  | rw  | rw    | rw   | rw      | rw  |          | rw           | rw     | rw   | rw | rw    | rw      | rw   |

| 15       | 14          | 13  | 12  | 11    | 10   | 9       | 8   | 7        | 6            | 5      | 4    | 3  | 2     | 1       | 0    |

|          | reser       | wod |     | ALIGN | EOCS | DDS     | DMA |          |              | Reserv | vod. |    |       | CONT    | ADON |

|          | 16261       | veu |     | rw    | rw   | rw      | rw  |          |              | Neserv | cu   |    |       | rw      | rw   |

Bit 31 Reserved, must be kept at reset value.

## Bit 30 **SWSTART:** Start conversion of regular channels

This bit is set by software to start conversion and cleared by hardware as soon as the conversion starts.

0: Reset state

1: Starts conversion of regular channels

Note: This bit can be set only when ADON = 1 otherwise no conversion is launched.

## Bits 29:28 **EXTEN:** External trigger enable for regular channels

These bits are set and cleared by software to select the external trigger polarity and enable the trigger of a regular group.

00: Trigger detection disabled

01: Trigger detection on the rising edge

10: Trigger detection on the falling edge

11: Trigger detection on both the rising and falling edges

# Bits 27:24 EXTSEL[3:0]: External event select for regular group

These bits select the external event used to trigger the start of conversion of a regular group:

0000: Timer 1 CC1 event

0001: Timer 1 CC2 event

0010: Timer 1 CC3 event

0011: Timer 2 CC2 event

0100: Timer 2 CC3 event 0101: Timer 2 CC4 event

0110: Timer 2 TRGO event

0111: Timer 3 CC1 event

1000: Timer 3 TRGO event

1001: Timer 4 CC4 event

1010: Timer 5 CC1 event

1011: Timer 5 CC2 event

1100: Timer 5 CC3 event

1101: Timer 8 CC1 event

1110: Timer 8 TRGO event

1111: EXTI line11

Bit 23 Reserved, must be kept at reset value.

577

### Bit 22 JSWSTART: Start conversion of injected channels

This bit is set by software and cleared by hardware as soon as the conversion starts.

0: Reset state

1: Starts conversion of injected channels

Note: This bit can be set only when ADON = 1 otherwise no conversion is launched.

### Bits 21:20 **JEXTEN:** External trigger enable for injected channels

These bits are set and cleared by software to select the external trigger polarity and enable the trigger of an injected group.

00: Trigger detection disabled

01: Trigger detection on the rising edge

10: Trigger detection on the falling edge

11: Trigger detection on both the rising and falling edges

### Bits 19:16 JEXTSEL[3:0]: External event select for injected group

These bits select the external event used to trigger the start of conversion of an injected group.

0000: Timer 1 CC4 event

0001: Timer 1 TRGO event

0010: Timer 2 CC1 event

0011: Timer 2 TRGO event

0100: Timer 3 CC2 event

0101: Timer 3 CC4 event

0110: Timer 4 CC1 event

0111: Timer 4 CC2 event 1000: Timer 4 CC3 event

1001: Timer 4 TRGO event

1010: Timer 5 CC4 event

1011: Timer 5 TRGO event

1100: Timer 8 CC2 event

1101: Timer 8 CC3 event

1110: Timer 8 CC4 event

1111: EXTI line15

#### Bits 15:12 Reserved, must be kept at reset value.

#### Bit 11 ALIGN: Data alignment

This bit is set and cleared by software. Refer to Figure 48 and Figure 49.

0: Right alignment

1: Left alignment

## Bit 10 EOCS: End of conversion selection

This bit is set and cleared by software.

0: The EOC bit is set at the end of each sequence of regular conversions. Overrun detection is enabled only if DMA=1.

1: The EOC bit is set at the end of each regular conversion. Overrun detection is enabled.

### Bit 9 DDS: DMA disable selection (for single ADC mode)

This bit is set and cleared by software.

0: No new DMA request is issued after the last transfer (as configured in the DMA controller)

1: DMA requests are issued as long as data are converted and DMA=1

### Bit 8 **DMA:** Direct memory access mode (for single ADC mode)

This bit is set and cleared by software. Refer to the DMA controller chapter for more details.

0: DMA mode disabled

1: DMA mode enabled

## Bits 7:2 Reserved, must be kept at reset value.

#### Bit 1 CONT: Continuous conversion

This bit is set and cleared by software. If it is set, conversion takes place continuously until it is cleared.

0: Single conversion mode

1: Continuous conversion mode

#### Bit 0 ADON: A/D Converter ON / OFF

This bit is set and cleared by software.

Note: 0: Disable ADC conversion and go to power down mode

1: Enable ADC

# 13.13.4 ADC sample time register 1 (ADC\_SMPR1)

Address offset: 0x0C

Reset value: 0x0000 0000

| 31      | 30                | 29      | 28 | 27 | 26      | 25      | 24 | 23       | 22       | 21 | 20       | 19       | 18 | 17       | 16     |

|---------|-------------------|---------|----|----|---------|---------|----|----------|----------|----|----------|----------|----|----------|--------|

|         | В                 | oconyod |    |    | 5       | MP18[2: | 0] | S        | MP17[2:0 | 0] | S        | MP16[2:0 | 0] | SMP1     | 5[2:1] |

|         | Reserved          |         |    |    | rw      | rw      | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw     |

| 15      | 14                | 13      | 12 | 11 | 10      | 9       | 8  | 7        | 6        | 5  | 4        | 3        | 2  | 1        | 0      |

| SMP15_0 | MP15_0 SMP14[2:0] |         |    | S  | MP13[2: | 0]      | S  | MP12[2:0 | )]       | S  | MP11[2:0 | 0]       | S  | MP10[2:0 | [0]    |

| rw      | rw                | rw      | rw | rw | rw      | rw      | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw     |

Bits 31: 27 Reserved, must be kept at reset value.

# Bits 26:0 SMPx[2:0]: Channel x sampling time selection

These bits are written by software to select the sampling time individually for each channel. During sampling cycles, the channel selection bits must remain unchanged.

Note: 000: 3 cycles 001: 15 cycles 010: 28 cycles 011: 56 cycles 100: 84 cycles 101: 112 cycles 110: 144 cycles 111: 480 cycles

# 13.13.5 ADC sample time register 2 (ADC\_SMPR2)

Address offset: 0x10

420/1718

Reset value: 0x0000 0000

| 31         | 30           | 29 | 28       | 27 | 26       | 25       | 24 | 23       | 22       | 21 | 20       | 19       | 18 | 17       | 16     |

|------------|--------------|----|----------|----|----------|----------|----|----------|----------|----|----------|----------|----|----------|--------|

| Rese       | nvod         | ,  | SMP9[2:0 | ]  |          | SMP8[2:0 | ]  | ;        | SMP7[2:0 | ]  | ;        | SMP6[2:0 | ]  | SMP      | 5[2:1] |

| Nese       | riveu        | rw | rw       | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw     |

| 15         | 14           | 13 | 12       | 11 | 10       | 9        | 8  | 7        | 6        | 5  | 4        | 3        | 2  | 1        | 0      |

| SMP<br>5_0 | SMP4[2:0] SM |    |          |    | SMP3[2:0 | 0]       | ;  | SMP2[2:0 | ]        | ;  | SMP1[2:0 | ]        |    | SMP0[2:0 | ]      |

| rw         | rw           | rw | rw       | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw       | rw | rw       | rw     |

DocID018909 Rev 8

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:0 **SMPx[2:0]:** Channel x sampling time selection

These bits are written by software to select the sampling time individually for each channel. During sample cycles, the channel selection bits must remain unchanged.

Note: 000: 3 cycles 001: 15 cycles 010: 28 cycles 011: 56 cycles 100: 84 cycles 101: 112 cycles 110: 144 cycles

111: 480 cycles

# 13.13.6 ADC injected channel data offset register x (ADC\_JOFRx) (x=1..4)

Address offset: 0x14-0x20 Reset value: 0x0000 0000

| 31             | 30   | 29   | 28 | 27 | 26 | 25 | 24  | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----------------|------|------|----|----|----|----|-----|--------|----|----|----|----|----|----|----|

|                |      |      |    |    |    |    | Res | served |    |    |    |    |    |    |    |

| 15             | 14   | 13   | 12 | 11 | 10 | 9  | 8   | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| JOFFSETx[11:0] |      |      |    |    |    |    |     |        |    |    |    |    |    |    |    |

|                | Rese | iveu | •  | rw | rw | rw | rw  | rw     | rw | rw | rw | rw | rw | rw | rw |

Bits 31:12 Reserved, must be kept at reset value.

## Bits 11:0 JOFFSETx[11:0]: Data offset for injected channel x

These bits are written by software to define the offset to be subtracted from the raw converted data when converting injected channels. The conversion result can be read from in the ADC\_JDRx registers.

# 13.13.7 ADC watchdog higher threshold register (ADC\_HTR)

Address offset: 0x24

Reset value: 0x0000 0FFF

| 31 | 30   | 29    | 28 | 27 | 26 | 25 | 24  | 23     | 22  | 21    | 20 | 19 | 18 | 17 | 16 |

|----|------|-------|----|----|----|----|-----|--------|-----|-------|----|----|----|----|----|

|    |      |       |    |    |    |    | Res | served |     |       |    |    |    |    |    |

| 15 | 14   | 13    | 12 | 11 | 10 | 9  | 8   | 7      | 6   | 5     | 4  | 3  | 2  | 1  | 0  |

|    | Rese | n rod |    |    |    |    |     |        | НТ[ | 11:0] |    |    |    |    |    |

|    | Rese | iveu  |    | rw | rw | rw | rw  | rw     | rw  | rw    | rw | rw | rw | rw | rw |

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 HT[11:0]: Analog watchdog higher threshold

These bits are written by software to define the higher threshold for the analog watchdog.

#### 13.13.8 ADC watchdog lower threshold register (ADC\_LTR)

Address offset: 0x28

Reset value: 0x0000 0000

| 31       | 30   | 29   | 28 | 27 | 26 | 25 | 24  | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----------|------|------|----|----|----|----|-----|--------|----|----|----|----|----|----|----|

|          |      |      |    |    |    |    | Res | served |    |    |    |    |    |    |    |

| 15       | 14   | 13   | 12 | 11 | 10 | 9  | 8   | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| LT[11:0] |      |      |    |    |    |    |     |        |    |    |    |    |    |    |    |

|          | Rese | iveu |    | rw | rw | rw | rw  | rw     | rw | rw | rw | rw | rw | rw | rw |

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 LT[11:0]: Analog watchdog lower threshold

These bits are written by software to define the lower threshold for the analog watchdog.

#### 13.13.9 ADC regular sequence register 1 (ADC\_SQR1)

Address offset: 0x2C

Reset value: 0x0000 0000

| 31     | 30        | 29 | 28   | 27    | 26 | 25 | 24 | 23        | 22  | 21   | 20 | 19 | 18       | 17     | 16 |

|--------|-----------|----|------|-------|----|----|----|-----------|-----|------|----|----|----------|--------|----|

|        |           |    | Pos  | erved |    |    |    |           | L[3 | 3:0] |    |    | SQ1      | 6[4:1] |    |

|        |           |    | 1/69 | civeu |    |    |    | rw        | rw  | rw   | rw | rw | rw       | rw     | rw |

| 15     | 14        | 13 | 12   | 11    | 10 | 9  | 8  | 7         | 6   | 5    | 4  | 3  | 2        | 1      | 0  |

| SQ16_0 | SQ15[4:0] |    |      |       |    |    |    | SQ14[4:0] |     |      |    |    | SQ13[4:0 | ]      |    |

| rw     | rw        | rw | rw   | rw    | rw | rw | rw |           |     |      | rw | rw | rw       | rw     | rw |

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:20 L[3:0]: Regular channel sequence length

These bits are written by software to define the total number of conversions in the regular channel conversion sequence.

0000: 1 conversion 0001: 2 conversions

1111: 16 conversions

Bits 19:15 SQ16[4:0]: 16th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 16th in the conversion sequence.

Bits 14:10 SQ15[4:0]: 15th conversion in regular sequence

Bits 9:5 SQ14[4:0]: 14th conversion in regular sequence

Bits 4:0 SQ13[4:0]: 13th conversion in regular sequence

# 13.13.10 ADC regular sequence register 2 (ADC\_SQR2)

Address offset: 0x30

Reset value: 0x0000 0000

| 31     | 30   | 29       | 28 | 27       | 26 | 25 | 24 | 23       | 22       | 21 | 20 | 19 | 18       | 17     | 16 |

|--------|------|----------|----|----------|----|----|----|----------|----------|----|----|----|----------|--------|----|

| Rese   | nuod |          | ;  | SQ12[4:0 | )] |    |    |          | SQ11[4:0 | ]  |    |    | SQ1      | 0[4:1] |    |

| Rese   | iveu | rw rw rw |    |          |    |    | rw | rw       | rw       | rw | rw | rw | rw       | rw     | rw |

| 15     | 14   | 13       | 12 | 11       | 10 | 9  | 8  | 7        | 6        | 5  | 4  | 3  | 2        | 1      | 0  |

| SQ10_0 |      | SQ9[4:0] |    |          |    |    |    | SQ8[4:0] |          |    |    |    | SQ7[4:0] |        |    |

| rw     | rw   | rw       | rw | rw       | rw | rw | rw | rw       | rw       | rw | rw | rw | rw       | rw     | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:26 SQ12[4:0]: 12th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 12th in the sequence to be converted.

Bits 24:20 SQ11[4:0]: 11th conversion in regular sequence

Bits 19:15 SQ10[4:0]: 10th conversion in regular sequence

Bits 14:10 SQ9[4:0]: 9th conversion in regular sequence

Bits 9:5 **SQ8[4:0]:** 8th conversion in regular sequence

Bits 4:0 SQ7[4:0]: 7th conversion in regular sequence

# 13.13.11 ADC regular sequence register 3 (ADC\_SQR3)

Address offset: 0x34

Reset value: 0x0000 0000

| 31    | 30 29 28 27 26 |             |          |          | 26 | 25 | 24 | 23       | 22       | 21 | 20 | 19 | 18       | 17    | 16 |

|-------|----------------|-------------|----------|----------|----|----|----|----------|----------|----|----|----|----------|-------|----|

| Boos  | erved          |             |          | SQ6[4:0] |    |    |    |          | SQ5[4:0] |    |    |    | SQ4      | [4:1] |    |

| Rese  | erveu          | rw rw rw rw |          |          |    |    | rw | rw       | rw       | rw | rw | rw | rw       | rw    | rw |

| 15    | 14             | 13          | 12       | 11       | 10 | 9  | 8  | 7        | 6        | 5  | 4  | 3  | 2        | 1     | 0  |

| SQ4_0 |                |             | SQ3[4:0] |          |    |    |    | SQ2[4:0] |          |    |    |    | SQ1[4:0] |       |    |

| rw    | rw             | rw          | rw       | rw       | rw | rw | rw | rw       | rw       | rw | rw | rw | rw       | rw    | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:25 SQ6[4:0]: 6th conversion in regular sequence

These bits are written by software with the channel number (0..18) assigned as the 6th in the sequence to be converted.

Bits 24:20 SQ5[4:0]: 5th conversion in regular sequence

Bits 19:15 SQ4[4:0]: 4th conversion in regular sequence

Bits 14:10 SQ3[4:0]: 3rd conversion in regular sequence

Bits 9:5 SQ2[4:0]: 2nd conversion in regular sequence

Bits 4:0 SQ1[4:0]: 1st conversion in regular sequence

# 13.13.12 ADC injected sequence register (ADC\_JSQR)

Address offset: 0x38

Reset value: 0x0000 0000

| 31      | 30                     | 29 | 28 | 27   | 26    | 25 | 24 | 23 | 22 | 21  | 20   | 19 | 18       | 17     | 16 |

|---------|------------------------|----|----|------|-------|----|----|----|----|-----|------|----|----------|--------|----|

|         |                        |    |    | Pos  | erved |    |    |    |    | JL[ | 1:0] |    | JSQ      | 4[4:1] |    |

|         |                        |    |    | 1769 | civeu |    |    |    |    | rw  | rw   | rw | rw       | rw     | rw |

| 15      | 14                     | 13 | 12 | 11   | 10    | 9  | 8  | 7  | 6  | 5   | 4    | 3  | 2        | 1      | 0  |

| JSQ4[0] | 0] JSQ3[4:0] JSQ2[4:0] |    |    |      |       |    |    |    |    |     |      |    | JSQ1[4:0 | ]      |    |

| rw      | rw                     | rw | rw | rw   | rw    | rw | rw | rw | rw | rw  | rw   | rw | rw       | rw     | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:20 JL[1:0]: Injected sequence length

These bits are written by software to define the total number of conversions in the injected channel conversion sequence.

00: 1 conversion 01: 2 conversions 10: 3 conversions 11: 4 conversions

Bits 19:15 JSQ4[4:0]: 4th conversion in injected sequence (when JL[1:0]=3, see note below)

These bits are written by software with the channel number (0..18) assigned as the 4th in the sequence to be converted.

Bits 14:10 JSQ3[4:0]: 3rd conversion in injected sequence (when JL[1:0]=3, see note below)

Bits 9:5 JSQ2[4:0]: 2nd conversion in injected sequence (when JL[1:0]=3, see note below)

Bits 4:0 JSQ1[4:0]: 1st conversion in injected sequence (when JL[1:0]=3, see note below)

Note:

When JL[1:0]=3 (4 injected conversions in the sequencer), the ADC converts the channels in the following order: JSQ1[4:0], JSQ2[4:0], JSQ3[4:0], and JSQ4[4:0].

When JL=2 (3 injected conversions in the sequencer), the ADC converts the channels in the following order: JSQ2[4:0], JSQ3[4:0], and JSQ4[4:0].

When JL=1 (2 injected conversions in the sequencer), the ADC converts the channels in starting from JSQ3[4:0], and then JSQ4[4:0].

When JL=0 (1 injected conversion in the sequencer), the ADC converts only JSQ4[4:0] channel.

# 13.13.13 ADC injected data register x (ADC\_JDRx) (x= 1..4)

Address offset: 0x3C - 0x48 Reset value: 0x0000 0000

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24  | 23       | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----------|----|----|----|----|----|-----|----------|----|----|----|----|----|----|----|

|    | Reserved |    |    |    |    |    |     |          |    |    |    |    |    |    |    |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8   | 7        | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |          |    |    |    |    |    | JDA | TA[15:0] |    |    |    |    |    |    |    |

| r  | r        | r  | r  | r  | r  | r  | r   | r        | r  | r  | r  | r  | r  | r  | r  |

Bits 31:16 Reserved, must be kept at reset value.

#### Bits 15:0 JDATA[15:0]: Injected data

These bits are read-only. They contain the conversion result from injected channel x. The data are left -or right-aligned as shown in *Figure 48* and *Figure 49*.

# 13.13.14 ADC regular data register (ADC DR)

Address offset: 0x4C

Reset value: 0x0000 0000

| 31 | 30       | 29 | 28 | 27 | 26 | 25 | 24  | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----------|----|----|----|----|----|-----|---------|----|----|----|----|----|----|----|

|    | Reserved |    |    |    |    |    |     |         |    |    |    |    |    |    |    |

| 15 | 14       | 13 | 12 | 11 | 10 | 9  | 8   | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |          |    |    |    |    |    | DAT | A[15:0] |    |    |    |    |    |    |    |

| r  | r        | r  | r  | r  | r  | r  | r   | r       | r  | r  | r  | r  | r  | r  | r  |

Bits 31:16 Reserved, must be kept at reset value.

# Bits 15:0 DATA[15:0]: Regular data

These bits are read-only. They contain the conversion result from the regular channels. The data are left- or right-aligned as shown in *Figure 48* and *Figure 49*.

# 13.13.15 ADC Common status register (ADC\_CSR)

Address offset: 0x00 (this offset address is relative to ADC1 base address + 0x300)

Reset value: 0x0000 0000

This register provides an image of the status bits of the different ADCs. Nevertheless it is read-only and does not allow to clear the different status bits. Instead each status bit must be cleared by writing it to 0 in the corresponding ADC\_SR register.

| 31  | 30    | 29   | 28    | 27         | 26    | 25   | 24   | 23  | 22    | 21   | 20    | 19     | 18     | 17   | 16   |

|-----|-------|------|-------|------------|-------|------|------|-----|-------|------|-------|--------|--------|------|------|

|     |       |      |       |            |       |      |      |     |       | OVR3 | STRT3 | JSTRT3 | JEOC 3 | EOC3 | AWD3 |

|     |       |      |       | Res        |       |      | AD   | C3  |       |      |       |        |        |      |      |

|     |       |      |       |            |       |      |      |     |       | r    | r     | r      | r      | r    | r    |

| 15  | 14    | 13   | 12    | 11         | 10    | 9    | 8    | 7   | 6     | 5    | 4     | 3      | 2      | 1    | 0    |

|     |       | OVR2 | STRT2 | JSTRT<br>2 | JEOC2 | EOC2 | AWD2 |     |       | OVR1 | STRT1 | JSTRT1 | JEOC 1 | EOC1 | AWD1 |

| Res | erved |      |       | AD         | C2    |      |      | Res | erved |      |       | AD     | C1     |      |      |

|     |       | r    | r     | r          | r     | r    | r    |     |       | r    | r     | r      | r      | r    | r    |

Bits 31:22 Reserved, must be kept at reset value.

Bit 21 OVR3: Overrun flag of ADC3

This bit is a copy of the OVR bit in the ADC3\_SR register.

Bit 20 STRT3: Regular channel Start flag of ADC3

This bit is a copy of the STRT bit in the ADC3\_SR register.

- Bit 19 **JSTRT3:** Injected channel Start flag of ADC3

This bit is a copy of the JSTRT bit in the ADC3\_SR register.

- Bit 18 **JEOC3:** Injected channel end of conversion of ADC3

This bit is a copy of the JEOC bit in the ADC3\_SR register.

- Bit 17 **EOC3:** End of conversion of ADC3

This bit is a copy of the EOC bit in the ADC3 SR register.

- Bit 16 **AWD3:** Analog watchdog flag of ADC3

This bit is a copy of the AWD bit in the ADC3\_SR register.

- Bits 15:14 Reserved, must be kept at reset value.

- Bit 13 **OVR2**: Overrun flag of ADC2

This bit is a copy of the OVR bit in the ADC2\_SR register.

- Bit 12 **STRT2**: Regular channel Start flag of ADC2

This bit is a copy of the STRT bit in the ADC2 SR register.

- Bit 11 **JSTRT2:** Injected channel Start flag of ADC2

This bit is a copy of the JSTRT bit in the ADC2\_SR register.

- Bit 10 **JEOC2**: Injected channel end of conversion of ADC2

This bit is a copy of the JEOC bit in the ADC2\_SR register.

- Bit 9 **EOC2:** End of conversion of ADC2

This bit is a copy of the EOC bit in the ADC2\_SR register.

- Bit 8 **AWD2**: Analog watchdog flag of ADC2

This bit is a copy of the AWD bit in the ADC2 SR register.

- Bits 7:6 Reserved, must be kept at reset value.

- Bit 5 **OVR1:** Overrun flag of ADC1

This bit is a copy of the OVR bit in the ADC1\_SR register.

- Bit 4 **STRT1:** Regular channel Start flag of ADC1

This bit is a copy of the STRT bit in the ADC1\_SR register.

- Bit 3 **JSTRT1**: Injected channel Start flag of ADC1

This bit is a copy of the JSTRT bit in the ADC1\_SR register.

- Bit 2 **JEOC1**: Injected channel end of conversion of ADC1

This bit is a copy of the JEOC bit in the ADC1\_SR register.

- Bit 1 **EOC1:** End of conversion of ADC1

This bit is a copy of the EOC bit in the ADC1\_SR register.

- Bit 0 **AWD1**: Analog watchdog flag of ADC1

This bit is a copy of the AWD bit in the ADC1 SR register.

**57**/

426/1718 DocID018909 Rev 8

# 13.13.16 ADC common control register (ADC\_CCR)

Address offset: 0x04 (this offset address is relative to ADC1 base address + 0x300)

Reset value: 0x0000 0000

| 31  | 30     | 29  | 28    | 27    | 26   | 25     | 24     | 23      | 22       | 21 | 20    | 19    | 18       | 17  | 16   |

|-----|--------|-----|-------|-------|------|--------|--------|---------|----------|----|-------|-------|----------|-----|------|

|     |        |     | Pas   | erved |      |        |        | TSVREFE | VBATE    |    | Rese  | arved |          | ADO | CPRE |

|     |        |     | 1103  | erveu |      |        |        | rw rw   |          |    | 11030 | i veu |          | rw  | rw   |

| 15  | 14     | 13  | 12    | 11    | 10   | 9      | 8      | 7       | 6        | 5  | 4     | 3     | 2        | 1   | 0    |

| DMA | \[1:0] | DDS | Res.  |       | DELA | Y[3:0] | /[3:0] |         | eserved  |    |       |       | MULTI[4: | 0]  |      |

| rw  | rw     | rw  | 1,65. | rw    | rw   | rw     | rw     |         | reserved |    | rw    | rw    | rw       | rw  |      |

Bits 31:24 Reserved, must be kept at reset value.

# Bit 23 **TSVREFE**: Temperature sensor and V<sub>REFINT</sub> enable

This bit is set and cleared by software to enable/disable the temperature sensor and the  $V_{\mathsf{REFINT}}$  channel.

- 0: Temperature sensor and V<sub>REFINT</sub> channel disabled

- 1: Temperature sensor and V<sub>REFINT</sub> channel enabled

Note: On STM32F42x and STM32F43x devices, VBATE must be disabled when TSVREFE is set. If both bits are set, only the VBAT conversion is performed.

# Bit 22 VBATE: VBAT enable

This bit is set and cleared by software to enable/disable the  $V_{\mbox{\footnotesize{BAT}}}$  channel.

- 0: V<sub>BAT</sub> channel disabled

- 1: V<sub>BAT</sub> channel enabled

Bits 21:18 Reserved, must be kept at reset value.

# Bits 17:16 ADCPRE: ADC prescaler

Set and cleared by software to select the frequency of the clock to the ADC. The clock is common for all the ADCs.

Note: 00: PCLK2 divided by 2

01: PCLK2 divided by 4

10: PCLK2 divided by 6

11: PCLK2 divided by 8

### Bits 15:14 DMA: Direct memory access mode for multi ADC mode

This bit-field is set and cleared by software. Refer to the DMA controller section for more details.

- 00: DMA mode disabled

- 01: DMA mode 1 enabled (2 / 3 half-words one by one 1 then 2 then 3)

- 10: DMA mode 2 enabled (2 / 3 half-words by pairs 2&1 then 1&3 then 3&2)

- 11: DMA mode 3 enabled (2 / 3 bytes by pairs 2&1 then 1&3 then 3&2)

## Bit 13 DDS: DMA disable selection (for multi-ADC mode)

This bit is set and cleared by software.

- 0: No new DMA request is issued after the last transfer (as configured in the DMA controller). DMA bits are not cleared by hardware, however they must have been cleared and set to the wanted mode by software before new DMA requests can be generated.

- 1: DMA requests are issued as long as data are converted and DMA = 01, 10 or 11.

Bit 12 Reserved, must be kept at reset value.

### Bit 11:8 DELAY: Delay between 2 sampling phases

Set and cleared by software. These bits are used in dual or triple interleaved modes.

0000: 5 \* T<sub>ADCCLK</sub> 0001: 6 \* T<sub>ADCCLK</sub> 0010: 7 \* T<sub>ADCCLK</sub> ... 1111: 20 \* T<sub>ADCCLK</sub>

Bits 7:5 Reserved, must be kept at reset value.

### Bits 4:0 MULTI[4:0]: Multi ADC mode selection

These bits are written by software to select the operating mode.

All the ADCs independent: 00000: Independent mode

- 00001 to 01001: Dual mode, ADC1 and ADC2 working together, ADC3 is independent

00001: Combined regular simultaneous + injected simultaneous mode

00010: Combined regular simultaneous + alternate trigger mode

00011: Reserved

00101: Injected simultaneous mode only

00110: Regular simultaneous mode only

00111: interleaved mode only 01001: Alternate trigger mode only

- 10001 to 11001: Triple mode: ADC1, 2 and 3 working together

10001: Combined regular simultaneous + injected simultaneous mode

10010: Combined regular simultaneous + alternate trigger mode

10011: Reserved

10101: Injected simultaneous mode only

10110: Regular simultaneous mode only

10111: interleaved mode only

11001: Alternate trigger mode only

All other combinations are reserved and must not be programmed

Note: In multi mode, a change of channel configuration generates an abort that can cause a loss of synchronization. It is recommended to disable the multi ADC mode before any configuration change.

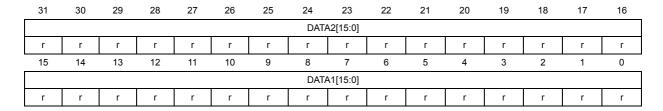

# 13.13.17 ADC common regular data register for dual and triple modes (ADC\_CDR)

Address offset: 0x08 (this offset address is relative to ADC1 base address + 0x300)

Reset value: 0x0000 0000

Bits 31:16 DATA2[15:0]: 2nd data item of a pair of regular conversions

- In dual mode, these bits contain the regular data of ADC2. Refer to *Dual ADC mode*.

- In triple mode, these bits contain alternatively the regular data of ADC2, ADC1 and ADC3.

Refer to *Triple ADC mode*.

Bits 15:0 DATA1[15:0]: 1st data item of a pair of regular conversions

- In dual mode, these bits contain the regular data of ADC1. Refer to Dual ADC mode

- In triple mode, these bits contain alternatively the regular data of ADC1, ADC3 and ADC2.

Refer to *Triple ADC mode*.

# 13.13.18 ADC register map

The following table summarizes the ADC registers.

Table 71. ADC global register map

| Offset        | Register         |

|---------------|------------------|

| 0x000 - 0x04C | ADC1             |

| 0x050 - 0x0FC | Reserved         |

| 0x100 - 0x14C | ADC2             |

| 0x118 - 0x1FC | Reserved         |

| 0x200 - 0x24C | ADC3             |

| 0x250 - 0x2FC | Reserved         |

| 0x300 - 0x308 | Common registers |

Table 72. ADC register map and reset values for each ADC

|        | ı                      |                      |          |      |          |     | <u> </u> |                      |          | - 1         |      |      |                    |     |                | aiue           |           |         |         | _     |         |      |           |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

|--------|------------------------|----------------------|----------|------|----------|-----|----------|----------------------|----------|-------------|------|------|--------------------|-----|----------------|----------------|-----------|---------|---------|-------|---------|------|-----------|------------------------------|-------|------|-------|------|------------|----------|---|---|----------|--------|------|--|---|---|---|

| Offset | Register               | 31                   | 29       | 28   | 27       | 25  | 24       | 23                   | 22       | 21          | 20   | 19   | 18                 | 7   | 16             | <del>5</del> 4 | 13        | 12      | 11      | 10    | 6       | ∞    | 7         | 9                            | 2     | 4    | 3     | 7    | -          | 0        |   |   |          |        |      |  |   |   |   |

| 0x00   | ADC_SR                 |                      |          |      |          |     |          |                      |          |             | Re   | ese  | erved              |     |                |                |           |         |         |       |         |      |           |                              | OVR   | STRT | JSTRT | JEOC | FOC        | AWD      |   |   |          |        |      |  |   |   |   |

|        | Reset value            | -                    |          |      |          |     |          |                      |          |             |      |      |                    |     |                |                |           |         |         |       |         |      |           |                              | 0     | 0    |       |      |            | 0        |   |   |          |        |      |  |   |   |   |

| 0x04   | ADC_CR1                | R                    | esen     | ved  | OVRIE    |     | KES[1:0] | AWDEN                | JAWDEN   |             | Re   | ese  | erved              |     | ı              | DIS(<br>) MUM  | C<br>2:0] | JDISCEN | DISCEN  | JAUTO | AWD SGL | SCAN | JEOCIE    | AWDIE                        | EOCIE | F    | WD    | CH[4 | 4:0]       |          |   |   |          |        |      |  |   |   |   |

|        | Reset value            |                      |          |      | 0        | 0   | 0        | 0                    | 0        |             |      |      |                    |     |                | 0 0            | 0         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x08   | ADC_CR2                | e e se de<br>SWSTART |          |      | EXTS     |     |          | Re<br>se<br>rv<br>ed | JSWSTART | JEXTEN[1:0] |      |      | EXT\$              | ]   |                | Rese           | erved     | d       |         |       | SQQ     | DMA  |           | F                            | Rese  | erve | d     |      |            | ADOIN    |   |   |          |        |      |  |   |   |   |

|        | Reset value            | 0                    | 0        | 0    | 0 0      | 0   | 0        |                      | 0        | 0           | 0    |      |                    | 0 ( |                |                |           |         | 0       | 0     |         | 0    |           |                              |       |      |       |      | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x0C   | ADC_SMPR1              |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                | oits SN        |           | _       |         |       |         |      |           |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

|        | Reset value            | 0 0                  | 0        | 0    | 0 0      | 0   | 0        | 0                    | 0        | 0           | 0    | 0    |                    | ) ( |                | 0 0            | 0         |         | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x10   | ADC_SMPR2              |                      | -        |      | 0 0      | 1 4 | T .      |                      |          | _           |      |      |                    |     |                | oits SN        |           |         | •       |       | _       |      | •         |                              | •     |      |       |      |            | _        |   |   |          |        |      |  |   |   |   |

|        | Reset value            | 0 0                  | 0        | 0    | 0 0      | 0   | 0        | 0                    | 0        | 0           | 0    | 0    | 0                  | ) ( | υ              | 0 0            | 0         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x14   | ADC_JOFR1              | _                    | Reserved |      |          |     |          |                      |          |             |      |      |                    |     | JOFFSET1[11:0] |                |           |         |         |       |         |      |           |                              |       | ٥Ι   | _     |      |            |          |   |   |          |        |      |  |   |   |   |

|        | Reset value  ADC_JOFR2 |                      | Reserved |      |          |     |          |                      |          |             |      |      |                    |     |                |                |           |         |         |       |         |      |           |                              |       |      |       | 0    | 0          | 0        | 0 | 0 | 0<br>FSE | 0<br>0 | 11:0 |  | 0 | 0 | 0 |

| 0x18   | Reset value            | _                    | Reserved |      |          |     |          |                      |          |             |      |      |                    |     |                |                | -         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | _    | 0     | 0    | 0          |          |   |   |          |        |      |  |   |   |   |

|        | ADC_JOFR3              |                      | Reserved |      |          |     |          |                      |          |             |      |      |                    |     |                |                |           | U       | U       | U     |         |      | FSE       |                              |       |      | 0     | ١    | _          |          |   |   |          |        |      |  |   |   |   |

| 0x1C   | Reset value            | =                    | Reserved |      |          |     |          |                      |          |             |      |      |                    |     |                |                | -         | 0       | 0       | 0     | 0       |      | 0         | 0                            | 0     |      | 0     | 0    | 0          |          |   |   |          |        |      |  |   |   |   |

|        | ADC_JOFR4              |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                |                |           |         |         |       |         |      | FSE       |                              |       |      |       |      | -          |          |   |   |          |        |      |  |   |   |   |

| 0x20   | Reset value            | _                    | Reserved |      |          |     |          |                      |          |             |      |      |                    |     |                |                | -         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          |          |   |   |          |        |      |  |   |   |   |

| 004    | ADC_HTR                |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                |                |           |         |         |       |         | HT[1 |           | ]                            |       |      | -     | ٦    |            |          |   |   |          |        |      |  |   |   |   |

| 0x24   | Reset value            | -                    |          |      |          |     |          | K                    | eser     | vec         | a    |      |                    |     |                |                |           |         | 1       | 1     | 1       | 1    | 1         | 1                            | 1     | 1    | 1     | 1    | 1          | 1        |   |   |          |        |      |  |   |   |   |

| 0x28   | ADC_LTR                |                      |          |      |          |     |          | P                    | eser     | NAV.        | 4    |      |                    |     |                |                |           |         |         |       |         |      |           | LT[1                         | 1:0   |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

| 0,20   | Reset value            |                      |          |      |          |     |          | IX                   | CSCI     | VEC         | J    |      |                    |     |                |                |           |         | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x2C   | ADC_SQR1               | _                    | F        | Rese | rved     |     |          |                      | L[3:     |             |      |      |                    |     |                |                | gular     |         |         |       |         |      |           |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

|        | Reset value            |                      |          |      |          |     |          | 0                    | 0        | 0           |      | 0    |                    | ) ( |                | 0 0            |           |         | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

|        | ADC_SQR2               | ved                  |          |      |          |     |          |                      |          |             | R    | legi | ular o             | han | inel           | seque          | ence      | SQ      | x_x     | bits  | 3       |      |           |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

| 0x30   | Reset value            | Reserved Reserved    | 0        | 0    | 0 0      | 0   | 0        | 0                    | 0        | 0           | 0    | 0    | 0                  | 0 0 | 0              | 0 0            | 0         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

|        | ADC_SQR3               | ved                  |          |      |          |     |          |                      |          |             | R    | legi | ular o             | han | nel            | seque          | ence      | SQ      | x_x     | bits  | 3       |      |           |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

| 0x34   | Reset value            | Reser                | 0        | 0    | 0 0      | 0   | 0        | 0                    | 0        | 0           | 0    | 0    | 0                  | 0   | 0              | 0 0            | 0         | 0       | 0       | 0     | 0       | 0    | 0         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x38   | ADC_JSQR               |                      |          | R    | eserv    | ed  |          |                      |          | -           | 1:0] |      |                    |     |                | Injed          |           |         |         |       |         |      |           | _                            |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

| 0,00   | Reset value            |                      |          |      | .0001 11 |     |          |                      |          | 0           | 0    | 0    | 0                  | 0 0 | 0              | 0 0            | 0         | 0       | 0       | 0     |         |      |           |                              | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x3C   | ADC_JDR1               |                      |          |      |          |     | Rese     | erved                | i        |             |      |      |                    |     |                |                |           |         |         |       |         | ATA  | -         |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

|        | Reset value            |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                | 0 0            | 0         | 0       | 0       | 0     |         | 0    |           |                              | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x40   | ADC_JDR2               | =                    |          |      |          |     | Rese     | ervec                | i        |             |      |      |                    |     | _              | 0 1 0          |           |         | ^       | •     |         | ATA  |           |                              | ^     |      | _     | 0    | <u>. Т</u> |          |   |   |          |        |      |  |   |   |   |

|        | Reset value            |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                | 0 0            | 0         | 0       | 0 0 0 0 |       |         |      |           | 0   0   0   0   0<br>A[15:0] |       |      |       |      | 0          | 0        |   |   |          |        |      |  |   |   |   |

| 0x44   | ADC_JDR3  Reset value  |                      |          |      |          | ı   | Rese     | ervec                | i        |             |      |      |                    |     |                | 0 0            | 0         | 0       | 0       | 0     |         | 0    | •         | 0                            | 0     | 0    | 0     | 0    | 0          | 0        |   |   |          |        |      |  |   |   |   |

|        | ADC_JDR4               |                      |          |      |          |     |          |                      |          |             |      |      |                    |     |                | 0 0            | J         | J       | v       | U     |         | ATA  |           |                              | U     | U    | ·     | ٥    | ٦          | $\dashv$ |   |   |          |        |      |  |   |   |   |

| 0x48   | Reset value            |                      | Reserved |      |          |     |          |                      |          |             |      |      | -                  | 0 0 | 0              | 0              | 0         | 0       |         |       | -       |      | 0         | 0                            | 0     | 0    | 0     | 0    |            |          |   |   |          |        |      |  |   |   |   |

|        | ADC_DR                 |                      |          |      |          |     |          |                      |          |             |      |      | Regular DATA[15:0] |     |                |                |           |         |         |       |         | -    | $\dot{-}$ |                              |       |      |       |      |            |          |   |   |          |        |      |  |   |   |   |

| 0x4C   | Reset value            | 1                    | Reserved |      |          |     |          |                      |          |             |      |      |                    | 0 0 | 0              | 0              | 0         | 0       | _       | 0     |         |      | •         | 0                            | 0     | 0    | 0     | 0    |            |          |   |   |          |        |      |  |   |   |   |

430/1718 DocID018909 Rev 8

Table 73. ADC register map and reset values (common ADC registers)

| Offset | Register    | 31              | 30      | 29 | 28   | 27       | 56        | 25 | 24 | 23      | 22    | 21  | 20   | 19    | 18   | 17          | 16  | 15       | 14  | 13      | 12       | 11    | 10   | 6    | 8   | 2  | 9    | 2   | 4    | 3     | 7      | 1    | 0   |

|--------|-------------|-----------------|---------|----|------|----------|-----------|----|----|---------|-------|-----|------|-------|------|-------------|-----|----------|-----|---------|----------|-------|------|------|-----|----|------|-----|------|-------|--------|------|-----|

| 000    | ADC_CSR     |                 |         |    | _    | <b>.</b> |           |    |    |         |       | OVR | STRT | JSTRT | JEOC | EOC         | AWD | Res      | er  | OVR     | STRT     | JSTRT | JEOC | EOC  | AWD | Re | ser  | OVR | STRT | JSTRT | JEOC   | EOC  | AWD |

| 0x00   | Reset value |                 |         |    | r    | kese     | erved     | J  |    |         |       | 0   | 0    | 0     | 0    | 0           | 0   | ve       | ved |         | 0        | 0     | 0    | 0    | 0   |    | ed   | 0   | 0    | 0     | 0      | 0    | 0   |

|        |             |                 | <u></u> |    |      |          |           |    |    |         |       |     |      | AD    | C3   |             |     |          |     |         |          | AD    | C2   |      |     |    |      |     |      | AD    | C1     |      |     |

| 0x04   | ADC_CCR     |                 |         | F  | Rese | erve     | d         |    |    | TSVREFE | VBATE | R   | lese | rve   | d    | ADCPREI1:01 |     | DMA[1:0] |     | DDS     | Reserved | DE    | ELΑ  | / [3 | :0] | Re | serv | /ed | ı    | MUI   | _T1 [- | 4:0] |     |

|        | Reset value |                 |         |    |      |          |           |    | 0  | 0       |       |     |      | 0 0   |      | 0           | 0   | 0 0 0    |     |         |          | 0     | 0    |      |     |    | 0    | 0   | 0    | 0     | 0      |      |     |

| 0x08   | ADC_CDR     | Regular D       |         |    | r D  | ATA:     | ΓA2[15:0] |    |    |         |       |     |      |       |      |             |     |          |     | Regular |          | ΑТА   | 1[15 | 5:0] |     |    |      |     |      |       |        |      |     |

| 0,00   | Reset value | 0 0 0 0 0 0 0 0 |         |    | 0    | 0        | 0         | 0  | 0  | 0       | 0     | 0   | 0    | 0     | 0    | 0           | 0   | 0        | 0   | 0       | 0        | 0     | 0    | 0    | 0   | 0  | 0    | 0   | 0    |       |        |      |     |

Refer to *Table 1 on page 64* for the register boundary addresses.