### **MICROPROCESSORS** From Assembly Language to C Using the PIC18Fxx2<sup>™</sup>

Robert B. Reese

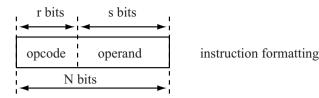

DA VINCI ENGINEERING PRESS

## MICROPROCESSORS

#### LIMITED WARRANTY AND DISCLAIMER OF LIABILITY

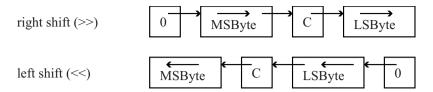

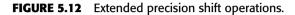

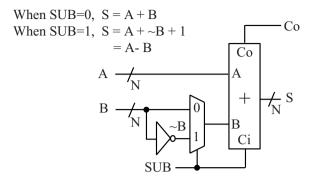

THE CD-ROM THAT ACCOMPANIES THE BOOK MAY BE USED ON A SINGLE PC ONLY. THE LICENSE DOES NOT PERMIT THE USE ON A NETWORK (OF ANY KIND). YOU FURTHER AGREE THAT THIS LICENSE GRANTS PERMISSION TO USE THE PRODUCTS CONTAINED HEREIN, BUT DOES NOT GIVE YOU RIGHT OF OWNERSHIP TO ANY OF THE CONTENT OR PRODUCT CONTAINED ON THIS CD-ROM. USE OF THIRD-PARTY SOFTWARE CONTAINED ON THIS CD-ROM IS LIMITED TO AND SUBJECT TO LICENSING TERMS FOR THE RESPECTIVE PROD-UCTS.

CHARLES RIVER MEDIA, INC. ("CRM") AND/OR ANYONE WHO HAS BEEN IN-VOLVED IN THE WRITING, CREATION, OR PRODUCTION OF THE ACCOMPANY-ING CODE ("THE SOFTWARE") OR THE THIRD-PARTY PRODUCTS CONTAINED ON THE CD-ROM OR TEXTUAL MATERIAL IN THE BOOK, CANNOT AND DO NOT WARRANT THE PERFORMANCE OR RESULTS THAT MAY BE OBTAINED BY USING THE SOFTWARE OR CONTENTS OF THE BOOK. THE AUTHOR AND PUBLISHER HAVE USED THEIR BEST EFFORTS TO ENSURE THE ACCURACY AND FUNCTION-ALITY OF THE TEXTUAL MATERIAL AND PROGRAMS CONTAINED HEREIN. WE HOWEVER, MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, RE-GARDING THE PERFORMANCE OF THESE PROGRAMS OR CONTENTS. THE SOFT-WARE IS SOLD "AS IS" WITHOUT WARRANTY (EXCEPT FOR DEFECTIVE MATERIALS USED IN MANUFACTURING THE DISK OR DUE TO FAULTY WORK-MANSHIP).

THE AUTHOR, THE PUBLISHER, DEVELOPERS OF THIRD-PARTY SOFTWARE, AND ANYONE INVOLVED IN THE PRODUCTION AND MANUFACTURING OF THIS WORK SHALL NOT BE LIABLE FOR DAMAGES OF ANY KIND ARISING OUT OF THE USE OF (OR THE INABILITY TO USE) THE PROGRAMS, SOURCE CODE, OR TEXTUAL MATERIAL CONTAINED IN THIS PUBLICATION. THIS INCLUDES, BUT IS NOT LIMITED TO, LOSS OF REVENUE OR PROFIT, OR OTHER INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OF THE PRODUCT.

THE SOLE REMEDY IN THE EVENT OF A CLAIM OF ANY KIND IS EXPRESSLY LIM-ITED TO REPLACEMENT OF THE BOOK AND/OR CD-ROM, AND ONLY AT THE DISCRETION OF CRM.

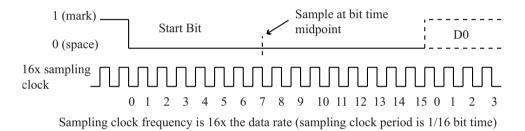

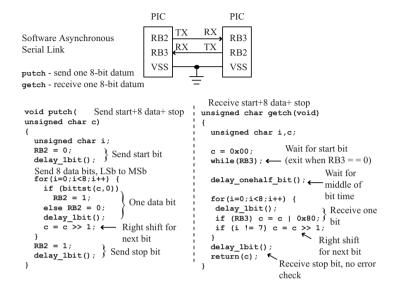

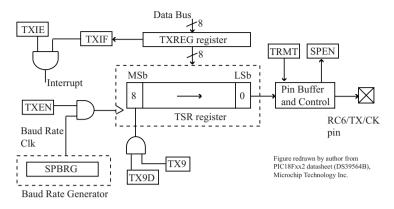

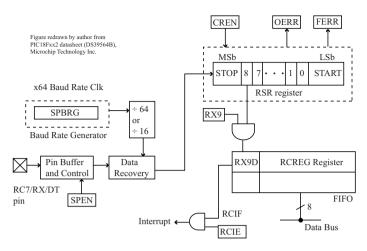

THE USE OF "IMPLIED WARRANTY" AND CERTAIN "EXCLUSIONS" VARIES FROM STATE TO STATE, AND MAY NOT APPLY TO THE PURCHASER OF THIS PRODUCT.

# MICROPROCESSORS FROM ASSEMBLY LANGUAGE TO C USING THE PIC18Fxx2<sup>®</sup>

**ROBERT B. REESE** MISSISSIPPI STATE UNIVERSTIY

DA VINCI ENGINEERING PRESS Hingham, Massachusetts Copyright 2005 by DA VINCI ENGINEERING PRESS, an imprint of CHARLES RIVER MEDIA, INC. All rights reserved.

Selected figures reprinted with permission of the copyright owner, Microchip Technology, Incorporated. All rights reserved. No further reprints or reproductions may be made without Microchip Technology Inc.'s prior written consent.

No part of this publication may be reproduced in any way, stored in a retrieval system of any type, or transmitted by any means or media, electronic or mechanical, including, but not limited to, photocopy, recording, or scanning, without prior permission in writing from the publisher.

Editor: David Pallai Cover Design: Tyler Creative

DA VINCI ENGINEERING PRESS CHARLES RIVER MEDIA, INC. 10 Downer Avenue Hingham, Massachusetts 02043 781-740-0400 781-740-8816 (FAX) info@charlesriver.com www.charlesriver.com This book is printed on acid-free paper.

Robert B. Reese. *Microprocessors: From Assembly Language to C Using the PIC18Fxx2*.

ISBN: 1-58450-378-5 eISBN: 1-58450-645-8

All brand names and product names mentioned in this book are trademarks or service marks of their respective companies. Any omission or misuse (of any kind) of service marks or trademarks should not be regarded as intent to infringe on the property of others. The publisher recognizes and respects all marks used by companies, manufacturers, and developers as a means to distinguish their products.

Library of Congress Cataloging-in-Publication Data Reese, Robert Bryan, 1958-

Microprocessors : from assembly language to C using the PIC18Fxx2 / Robert B. Reese. p. cm. Includes bibliographical references and index.

ISBN 1-58450-378-5 (hardcover with cd-rom : alk. paper)

1. Microprocessors. 2. Microprocessors. I. Title.

TK7895.M5R44 2005

#### 2005008835

Printed in the United States of America 05 7 6 5 4 3 2 First Edition

CHARLES RIVER MEDIA titles are available for site license or bulk purchase by institutions, user groups, corporations, etc. For additional information, please contact the Special Sales Department at 781-740-0400.

Requests for replacement of a defective CD-ROM must be accompanied by the original disc, your mailing address, telephone number, date of purchase, and purchase price. Please state the nature of the problem, and send the information to CHARLES RIVER MEDIA, INC., 10 Downer Avenue, Hingham, Massachusetts 02043. CRM's sole obligation to the purchaser is to replace the disc, based on defective materials or faulty workmanship, but not on the operation or functionality of the product.

To Donna, who puts up with me

This page intentionally left blank

# Contents

| Acknowledgments<br>Preface |                                                          |    |  |  |

|----------------------------|----------------------------------------------------------|----|--|--|

| 1                          | Number System and Digital Logic Review                   | 1  |  |  |

|                            | 1.1 Learning Objectives                                  | 1  |  |  |

|                            | 1.2 Binary Data                                          | 2  |  |  |

|                            | 1.3 Unsigned Number Conversion                           | 5  |  |  |

|                            | 1.4 Binary and Hex Arithmetic                            | 6  |  |  |

|                            | 1.5 Combinational Logic Functions                        | 10 |  |  |

|                            | 1.6 Combinational Building Blocks                        | 17 |  |  |

|                            | 1.7 Sequential Logic                                     | 21 |  |  |

|                            | 1.8 Sequential Building Blocks                           | 25 |  |  |

|                            | 1.9 Encoding Character Data                              | 27 |  |  |

|                            | Summary                                                  | 29 |  |  |

|                            | Review Exercises                                         | 29 |  |  |

| 2                          | The Stored Program Machine                               | 31 |  |  |

|                            | 2.1 Learning Objectives                                  | 31 |  |  |

|                            | 2.2 Problem Solving the Digital Way                      | 32 |  |  |

|                            | 2.3 Finite State Machine Design                          | 34 |  |  |

|                            | 2.4 A Stored Program Machine                             | 39 |  |  |

|                            | 2.5 Modern Computers                                     | 47 |  |  |

|                            | Summary                                                  | 47 |  |  |

|                            | Review Problems                                          | 47 |  |  |

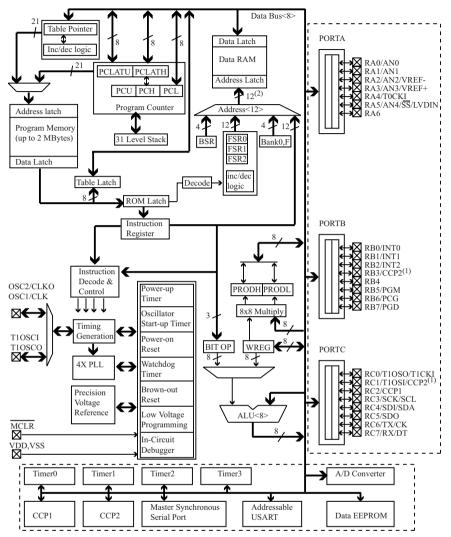

| 3                          | Introduction to the PIC18Fxx2                            | 51 |  |  |

|                            | 3.1 Learning Objectives                                  | 51 |  |  |

|                            | 3.2 Introduction to Microprocessors and Microcontrollers | 52 |  |  |

|                            | 3.3 The PIC18Fxx2 Microcontroller                        | 53 |  |  |

|                            | 3.4 Data Memory Organization and Data Transfer           | 55 |  |  |

|   | 3.5 Basic Arithmetic and Control Instructions              | 61  |

|---|------------------------------------------------------------|-----|

|   | 3.6 A PIC18 Assembly Language Program                      | 64  |

|   | 3.7 The Clock and Instruction Execution                    | 73  |

|   | Summary                                                    | 73  |

|   | Review Problems                                            | 74  |

| 4 | Unsigned 8-Bit Arithmetic, Logical, Conditional Operations | 77  |

|   | 4.1 Learning Objectives                                    | 77  |

|   | 4.2 Bitwise Logical Operations, Bit Operations             | 78  |

|   | 4.3 The STATUS Register                                    | 83  |

|   | 4.4 Unsigned Conditional Tests                             | 85  |

|   | 4.5 Looping                                                | 94  |

|   | 4.6 Shifts and Rotates                                     | 97  |

|   | Summary                                                    | 100 |

|   | Review Problems                                            | 100 |

| 5 | Extended Precision and Signed Operations                   | 103 |

|   | 5.1 Learning Objectives                                    | 103 |

|   | 5.2 Extended Precision Integers                            | 104 |

|   | 5.3 Extended Precision Operations                          | 105 |

|   | 5.4 Signed Number Representation                           | 114 |

|   | 5.5 Two's Complement Overflow                              | 119 |

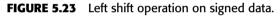

|   | 5.6 Operations on Signed Data                              | 120 |

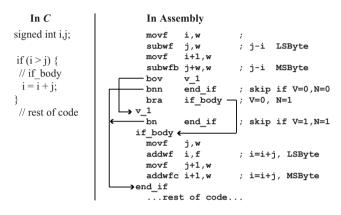

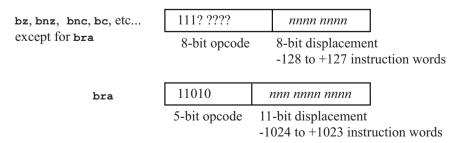

|   | 5.7 Branch Instruction Encoding                            | 127 |

|   | Summary                                                    | 129 |

|   | Review Problems                                            | 129 |

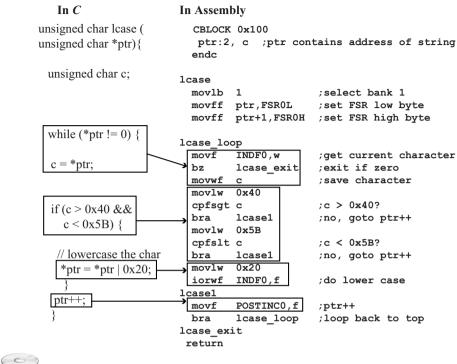

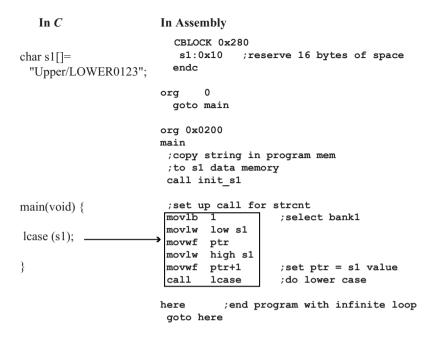

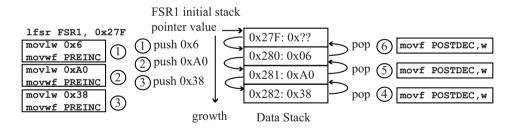

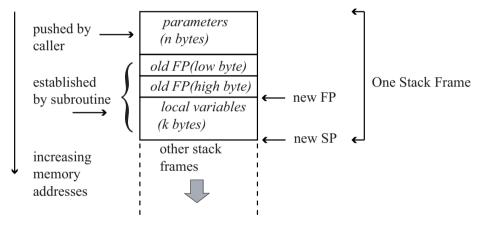

| 6 | Subroutines and Pointers                                   | 133 |

|   | 6.1 Learning Objectives                                    | 133 |

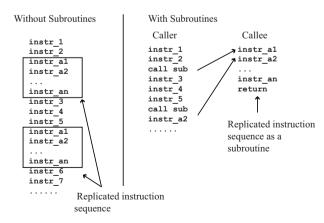

|   | 6.2 Subroutines                                            | 134 |

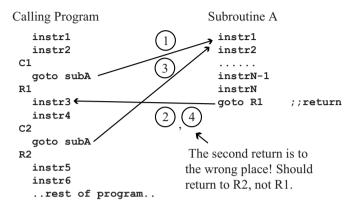

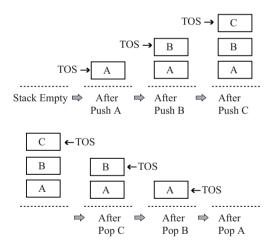

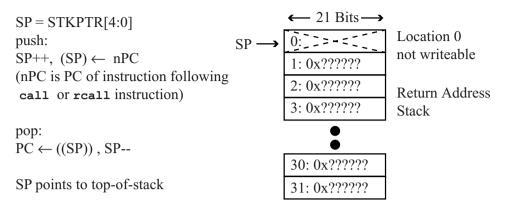

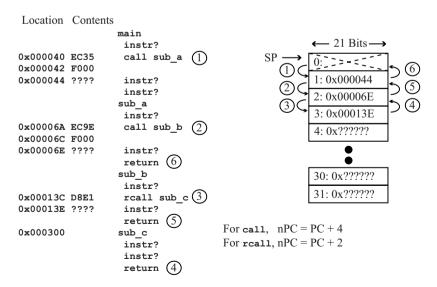

|   | 6.3 The Stack and Call/Return                              | 136 |

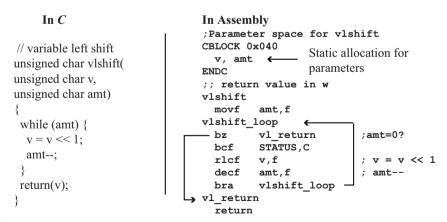

|   | 6.4 Implementing Subroutines in Assembly Language          | 141 |

|   | 6.5 Arrays and Pointers in <i>C</i>                        | 146 |

|   | 6.6 Arrays and Pointers in Assembly Language               | 152 |

|   | 6.7 Accessing Table Data from Program Memory               | 160 |

|   |                                                            |     |

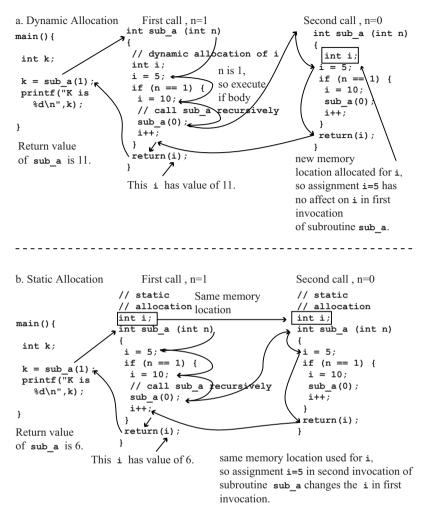

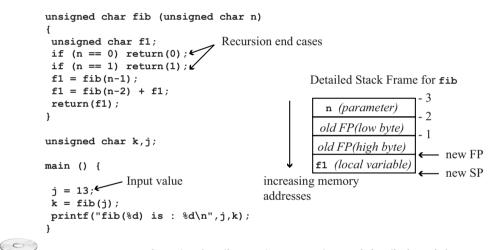

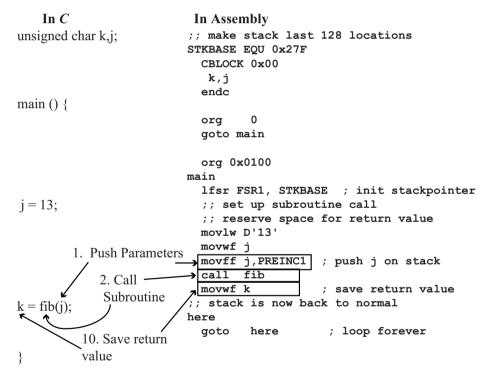

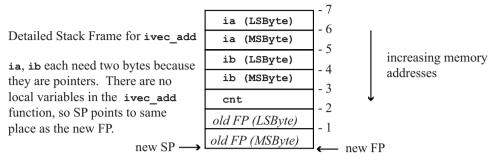

|   | 6.8 Subroutines and Stack Frames: Dynamic Allocation             | 162 |

|---|------------------------------------------------------------------|-----|

|   | Summary                                                          | 169 |

|   | Review Problems                                                  | 170 |

| 7 | Advanced Assembly Language: Higher Math                          | 175 |

|   | 7.1 Learning Objectives                                          | 175 |

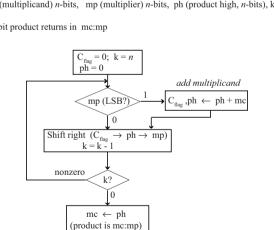

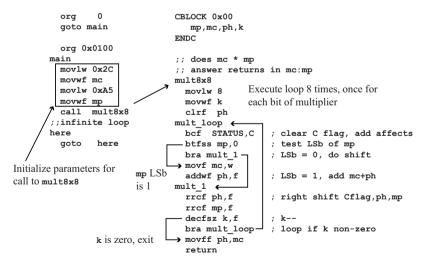

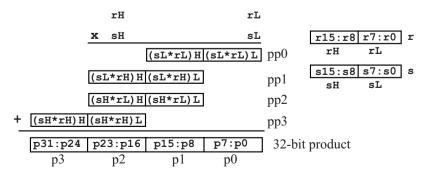

|   | 7.2 Multiplication                                               | 176 |

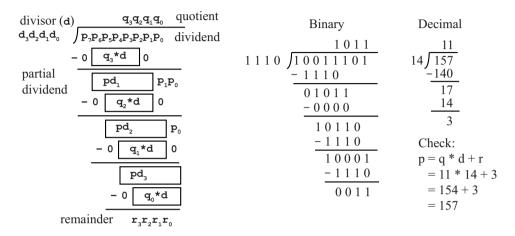

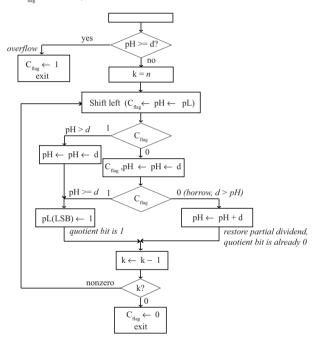

|   | 7.3 Division                                                     | 183 |

|   | 7.4 Fixed-Point and Saturating Arithmetic                        | 188 |

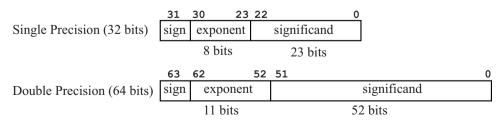

|   | 7.5 Floating-Point Number Representation                         | 192 |

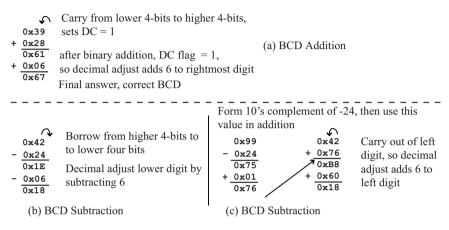

|   | 7.6 BCD Arithmetic                                               | 197 |

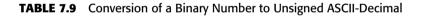

|   | 7.7 ASCII Data Conversion                                        | 199 |

|   | Summary                                                          | 204 |

|   | Review Problems                                                  | 204 |

| 8 | The PIC18Fxx2: System Startup and Parallel Port IO               | 207 |

|   | 8.1 Learning Objectives                                          | 207 |

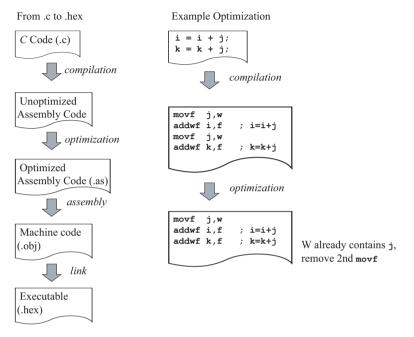

|   | 8.2 High-Level Languages versus Assembly Language                | 208 |

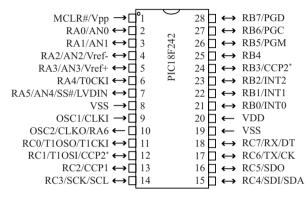

|   | 8.3 C Compilation for the PIC18F242                              | 210 |

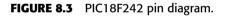

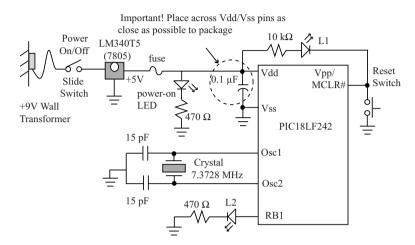

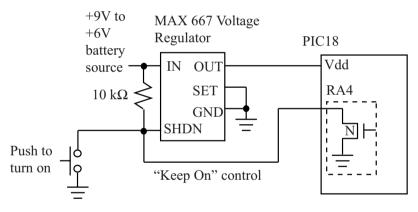

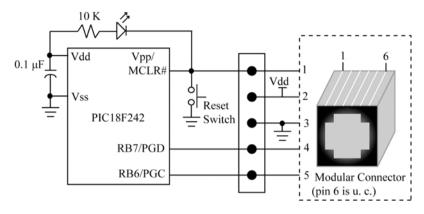

|   | 8.4 PIC18F242 Startup Schematic                                  | 216 |

|   | 8.5 <i>ledflash.c</i> –The First C Program for PIC18F242 Startup | 220 |

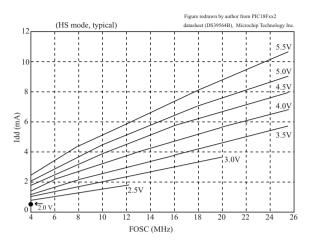

|   | 8.6 Datasheet Reading–A Critical Skill                           | 223 |

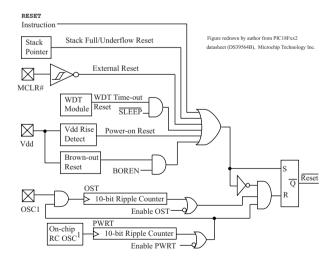

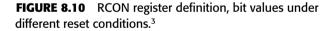

|   | 8.7 PIC18Fxx2 Reset Sources                                      | 225 |

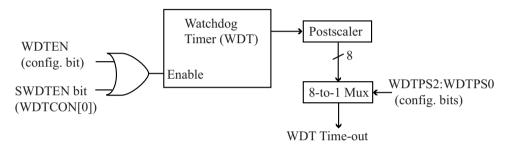

|   | 8.8 Experimenting with RESET, SLEEP, and the Watchdog Timer      | 228 |

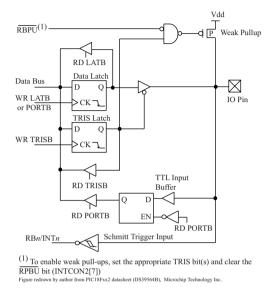

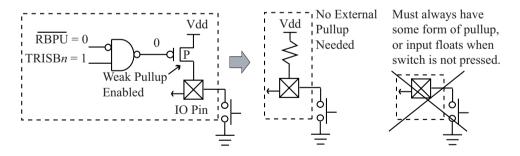

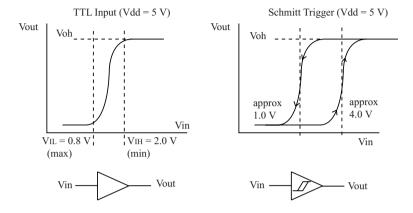

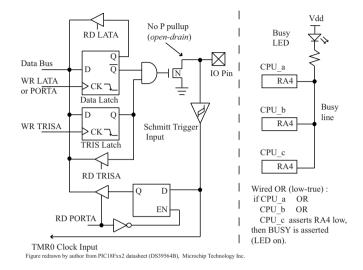

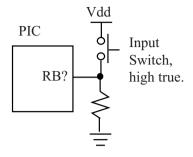

|   | 8.9 Parallel Port Operation                                      | 231 |

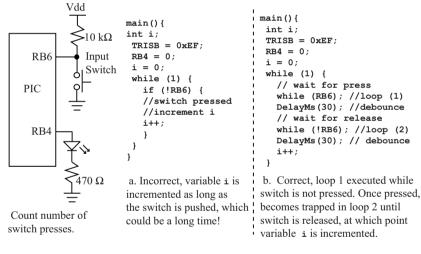

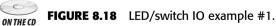

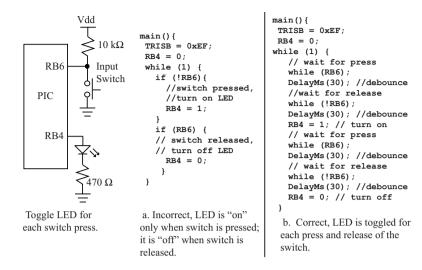

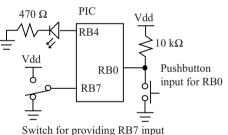

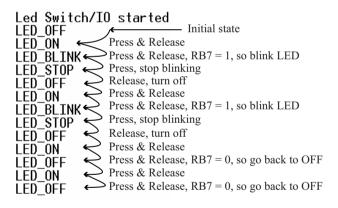

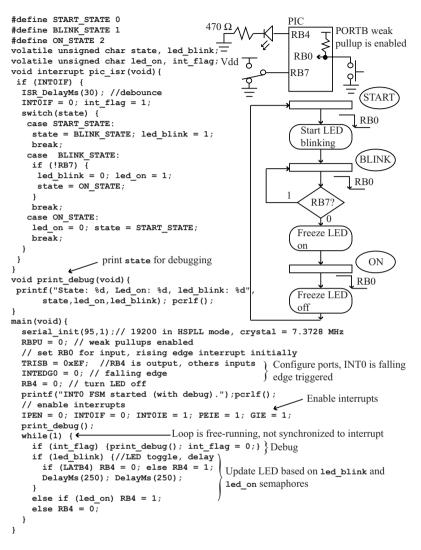

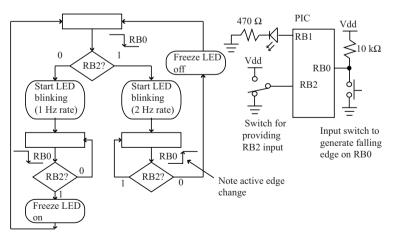

|   | 8.10 LED/Switch IO and State Machine Programming                 | 237 |

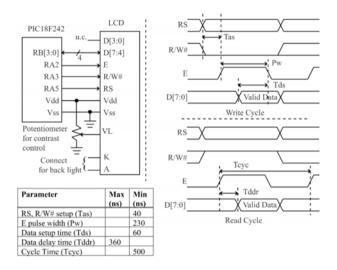

|   | 8.11 Interfacing to an LCD Module                                | 242 |

|   | Summary                                                          | 249 |

|   | Review Problems                                                  | 249 |

| 9 | Asynchronous Serial IO                                           | 253 |

|   | 9.1 Learning Objectives                                          | 253 |

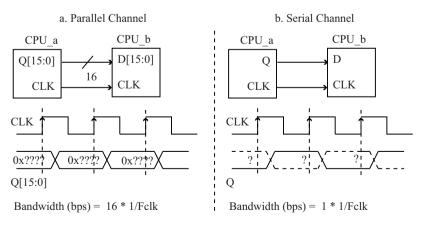

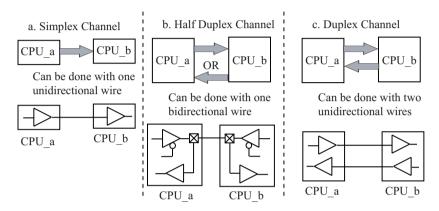

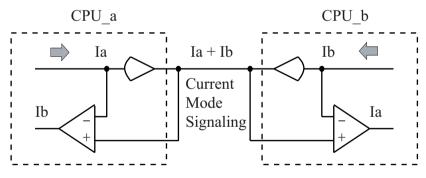

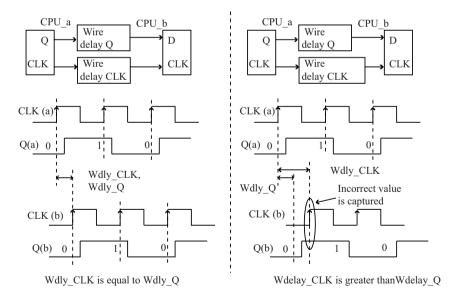

|   | 9.2 IO Channel Basics                                            | 254 |

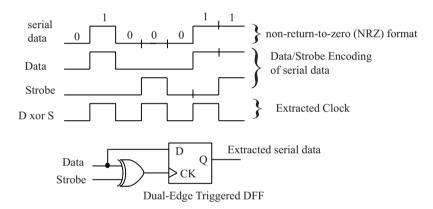

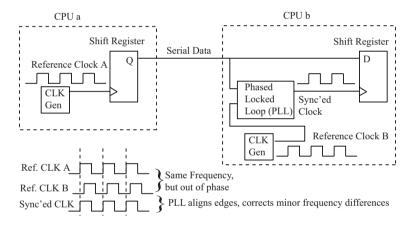

|   | 9.3 Synchronous Serial IO                                        | 257 |

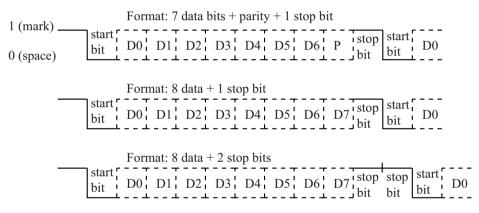

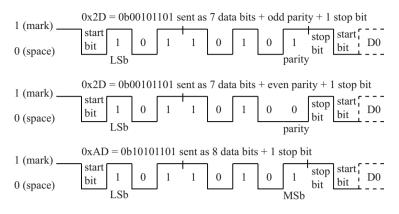

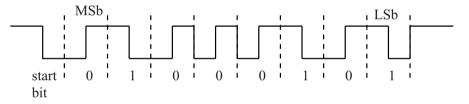

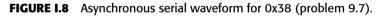

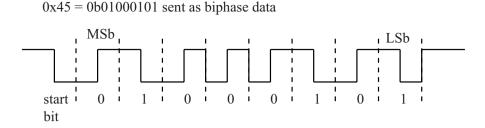

|   | 9.4 Asynchronous Serial IO                                       | 259 |

|    | 9.5 The PIC18Fxx2 USART                                        | 263 |

|----|----------------------------------------------------------------|-----|

|    | 9.6 The RS232 Standard                                         | 270 |

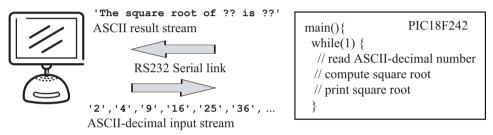

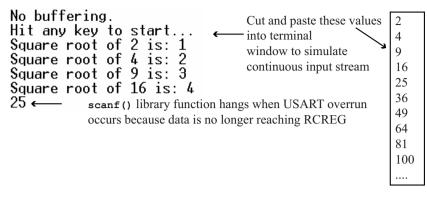

|    | 9.7 Serial IO Examples                                         | 273 |

|    | Summary                                                        | 277 |

|    | Review Problems                                                | 278 |

| 10 | Interrupts and a First Look at Timers                          | 281 |

|    | 10.1 Learning Objectives                                       | 281 |

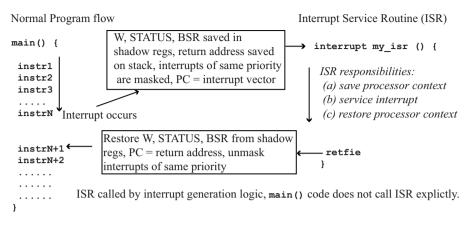

|    | 10.2 Interrupt Basics                                          | 282 |

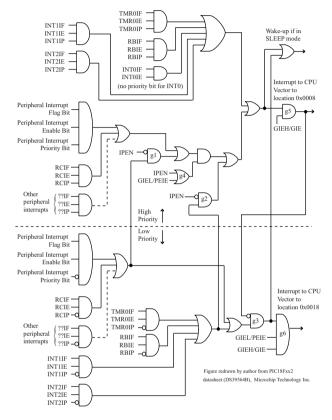

|    | 10.3 PIC18 Interrupt Details                                   | 284 |

|    | 10.4 Interrupt-Driven Asynchronous Serial Data Input           | 287 |

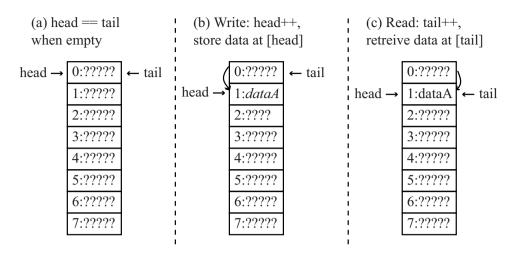

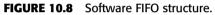

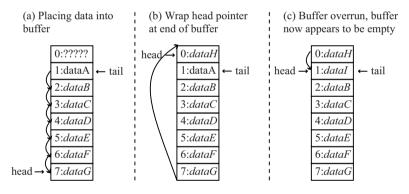

|    | 10.5 Using a Software FIFO with Interrupt-Driven IO            | 291 |

|    | 10.6 Other Interrupt Sources, Sleep Mode                       | 296 |

|    | 10.7 State Machine Programming for Interrupt-Driven IO         | 299 |

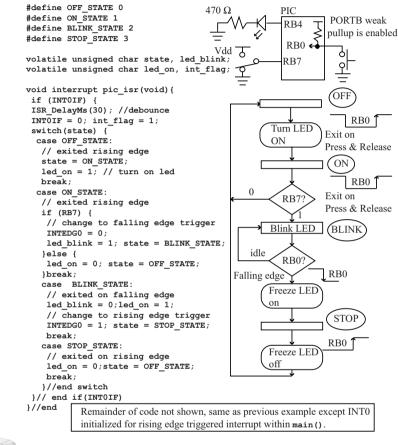

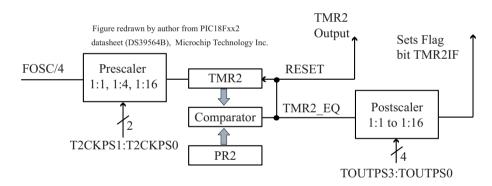

|    | 10.8 The Timer Subsystem: Timer2                               | 304 |

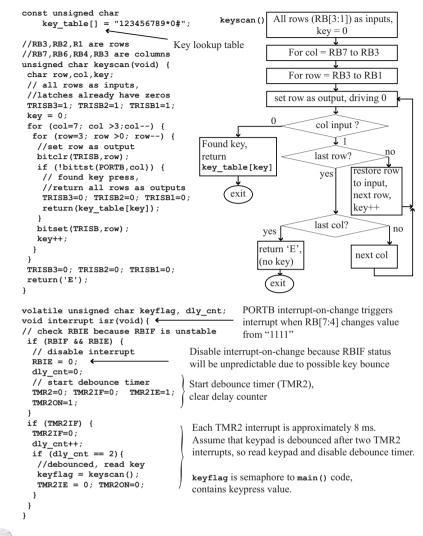

|    | 10.9 Switch Debouncing Using a Timer                           | 307 |

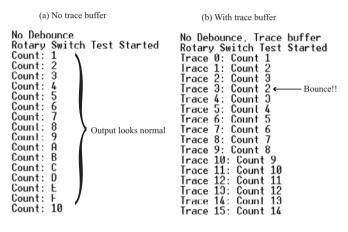

|    | 10.10 A Rotary Encoder Interface                               | 309 |

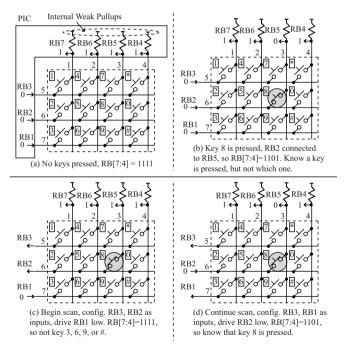

|    | 10.11 A Numeric Keypad Interface                               | 315 |

|    | 10.12 On Writing and Debugging ISRs                            | 319 |

|    | Summary                                                        | 321 |

|    | Review Problems                                                | 322 |

| 11 | Synchronous Serial IO                                          | 327 |

|    | 11.1 Learning Objectives                                       | 327 |

|    | 11.2 The PIC18 and Synchronous Serial IO                       | 328 |

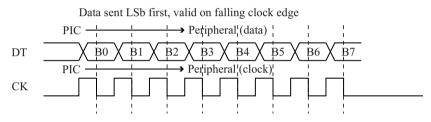

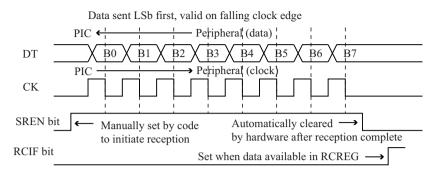

|    | 11.3 USART Synchronous Mode                                    | 329 |

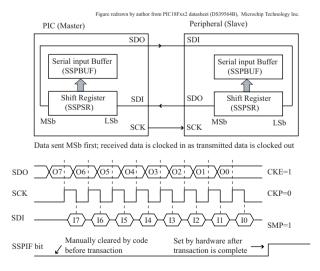

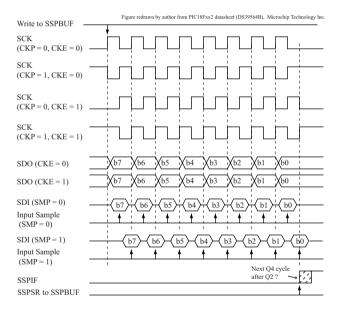

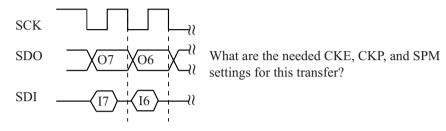

|    | 11.4 The Serial Peripheral Interface (SPI)                     | 331 |

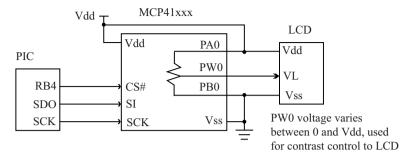

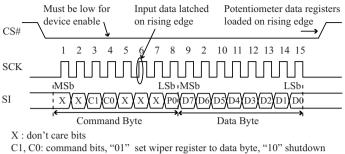

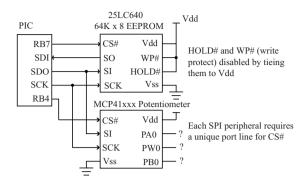

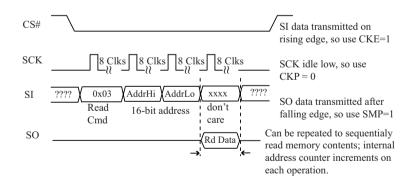

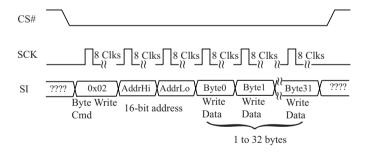

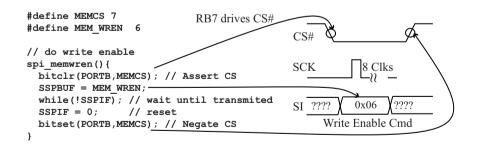

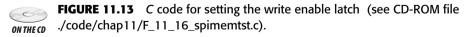

|    | 11.5 SPI Examples: A Digital Potentiometer and a Serial EEPROM | 334 |

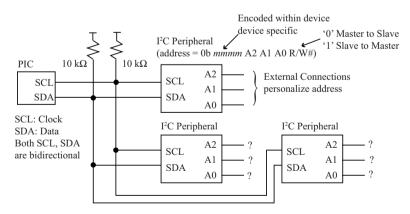

|    | 11.6 The I <sup>2</sup> C Bus                                  | 345 |

|    | 11.7 The I <sup>2</sup> C on the PIC18Fxx2                     | 348 |

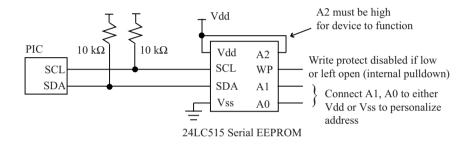

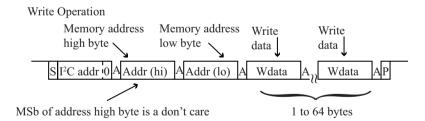

|    | 11.8 The 24LC515 Serial EEPROM                                 | 356 |

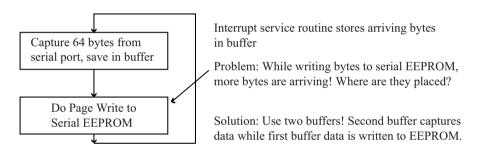

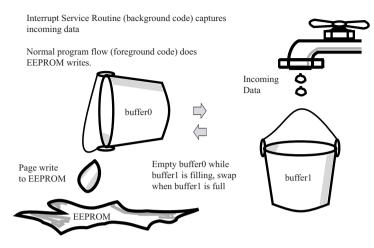

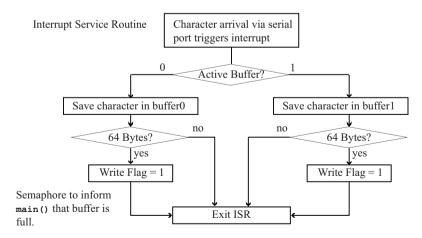

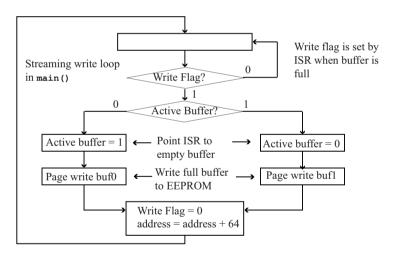

|    | 11.9 Double Buffering for Interrupt-Driven Writes              | 364 |

|    | Summary                                                        | 366 |

|    | Review Problems                                                | 367 |

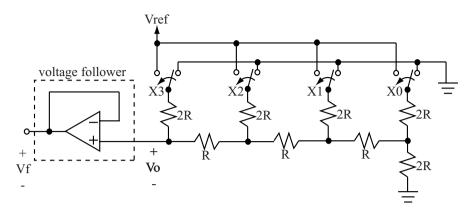

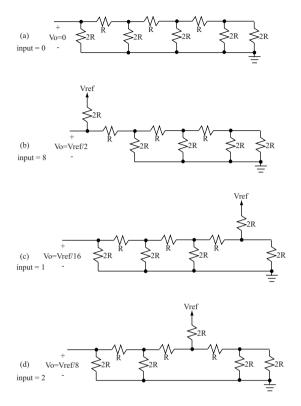

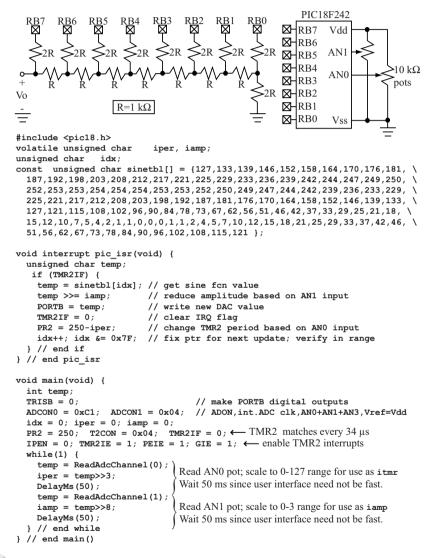

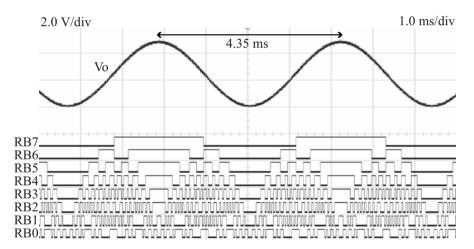

| 12 | Data Conversion                                         | 371 |

|----|---------------------------------------------------------|-----|

|    | 12.1 Learning Objectives                                | 371 |

|    | 12.2 Data Conversion Basics                             | 372 |

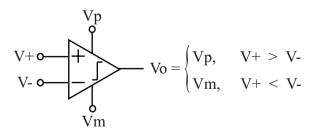

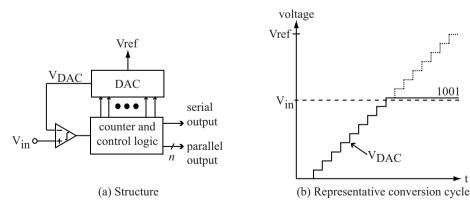

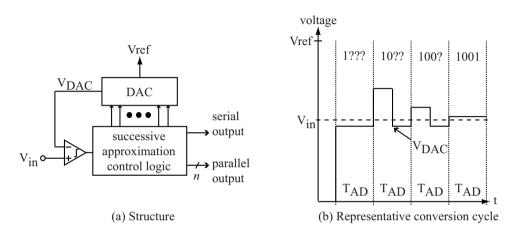

|    | 12.3 Analog-to-Digital Conversion                       | 373 |

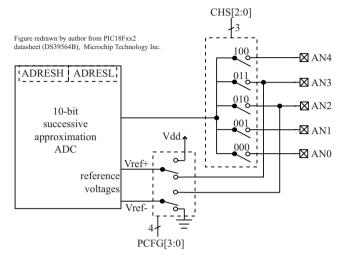

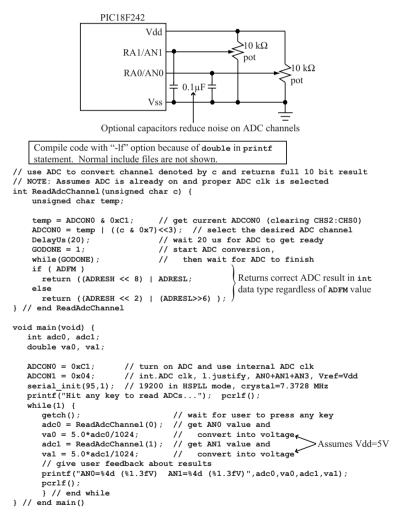

|    | 12.4 PIC18Fxx2 Analog-to-Digital Converter              | 382 |

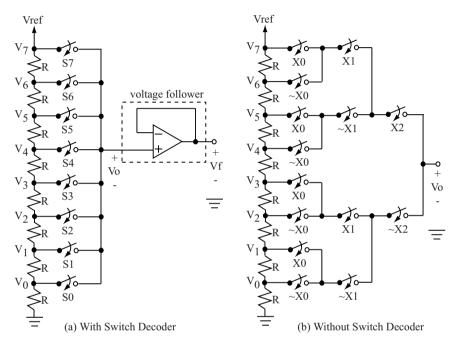

|    | 12.5 Digital-to-Analog Conversion                       | 391 |

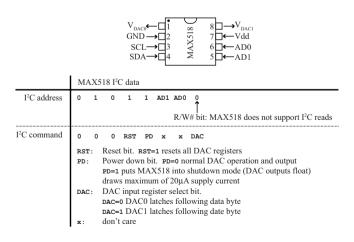

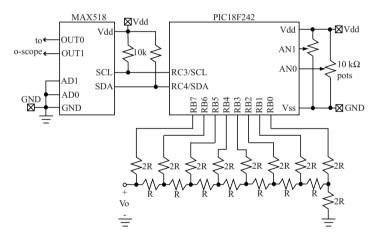

|    | 12.6 Digital-to-Analog Converter Example: The MAXIM 518 | 400 |

|    | Summary                                                 | 406 |

|    | Review Problems                                         | 407 |

| 13 | Timers                                                  | 411 |

|    | 13.1 Learning Objectives                                | 411 |

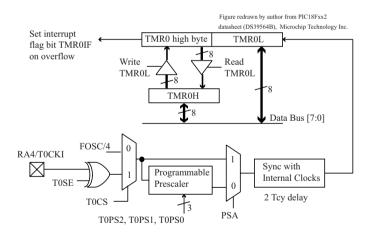

|    | 13.2 The Timer0 Subsystem                               | 412 |

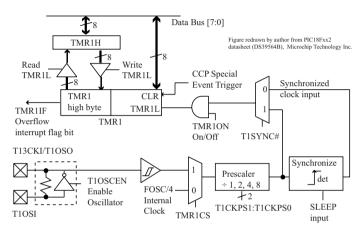

|    | 13.3 The Timer1 and Timer3 Subsystems                   | 419 |

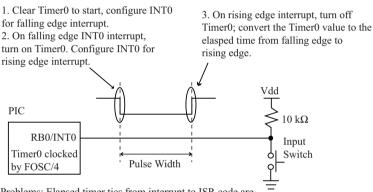

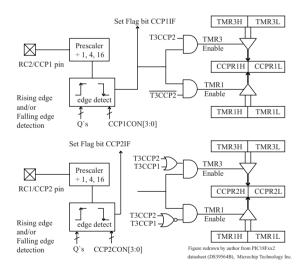

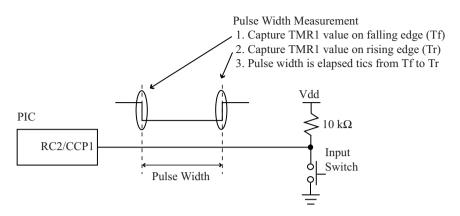

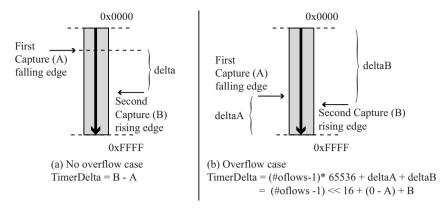

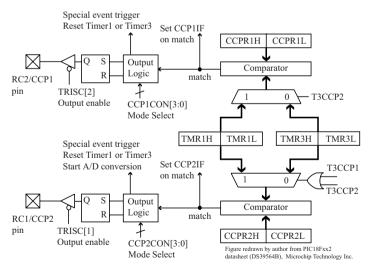

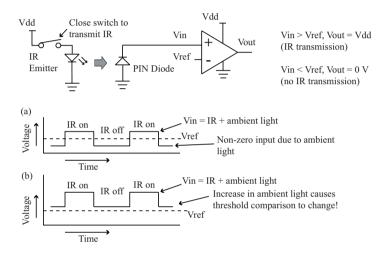

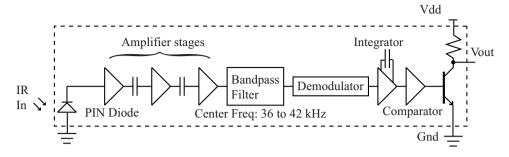

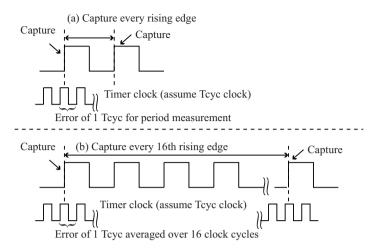

|    | 13.4 Pulse Width Measurement Using Capture Mode         | 422 |

|    | 13.5 Timer1/Timer3 Compare Mode                         | 428 |

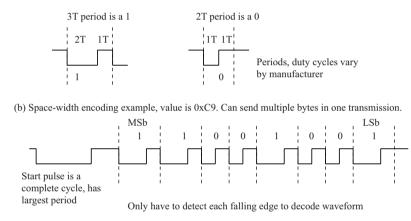

|    | 13.6 Using Capture Mode for Infrared Decoding           | 433 |

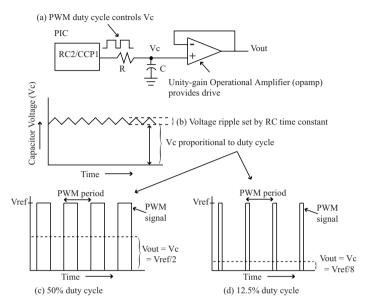

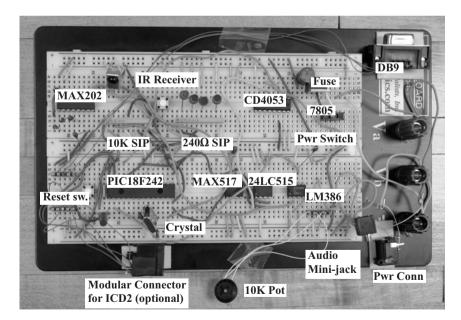

|    | 13.7 Timer2 and Pulse Width Modulation                  | 442 |

|    | 13.8 Using Capture Mode for Frequency Measurement       | 447 |

|    | Summary                                                 | 451 |

|    | Review Problems                                         | 452 |

| 14 | Capstone: Audio Sampling, Monitoring System,            |     |

|    | and Autonomous Robot                                    | 455 |

|    | 14.1 Learning Objectives                                | 456 |

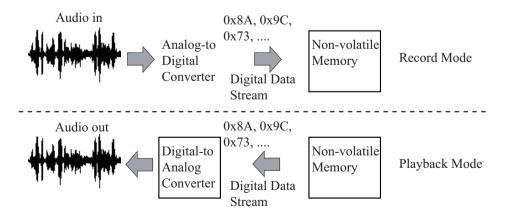

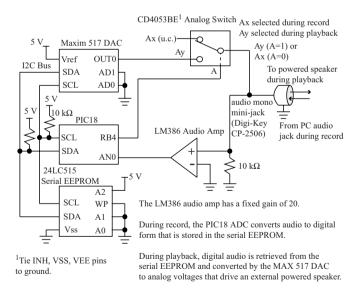

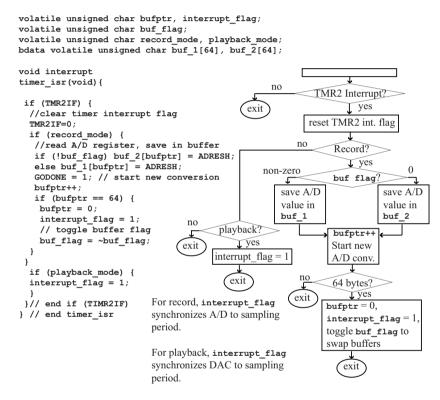

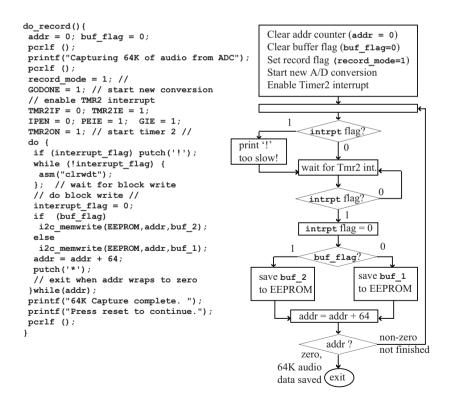

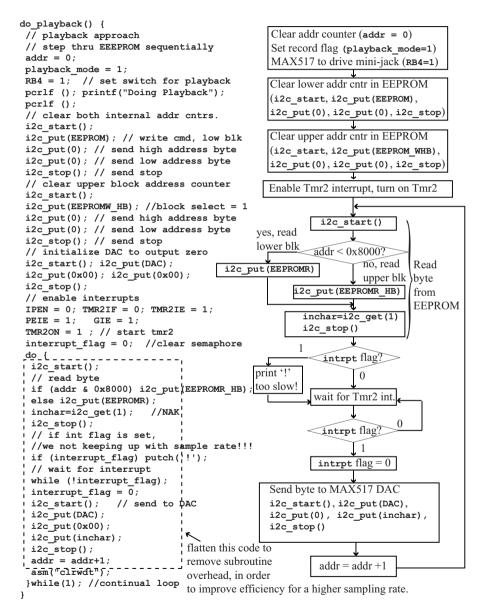

|    | 14.2 Design of an Audio Record/Playback System          | 456 |

|    | 14.3 Implementation of an Audio Record/Playback System  | 459 |

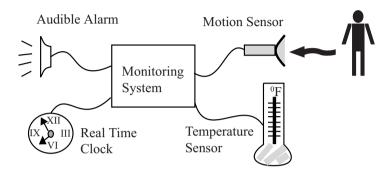

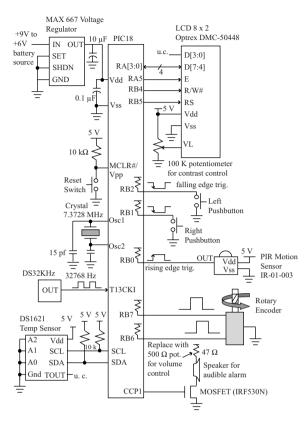

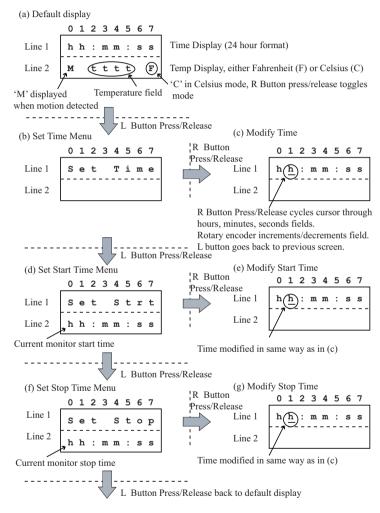

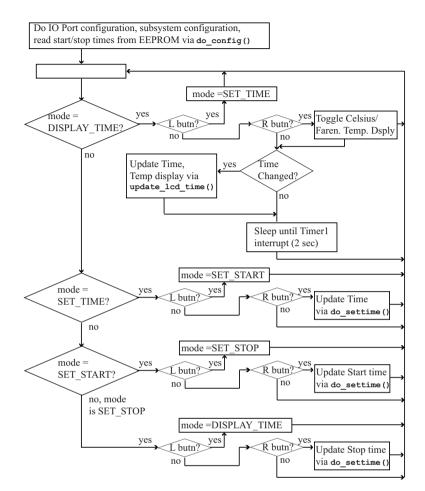

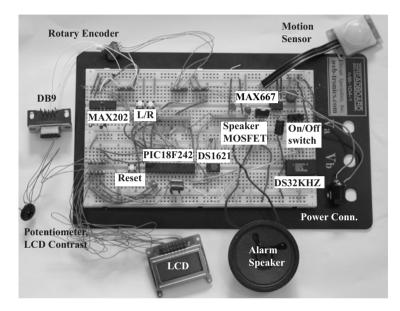

|    | 14.4 Design of a Home Monitoring System                 | 466 |

|    | 14.5 The DS1621 Digital Thermometer                     | 469 |

|    | 14.6 Using the Nonvolatile Storage on the PIC18Fxx2     | 475 |

| 14.6 Using the Nonvolatile Storage on the PIC18FXX2   | 4/5 |

|-------------------------------------------------------|-----|

| 14.7 Implementation of a Home Monitoring System       | 483 |

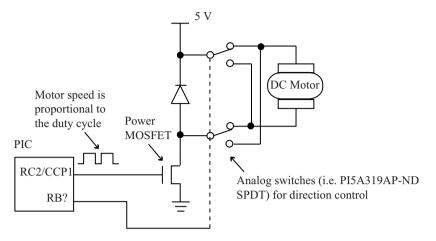

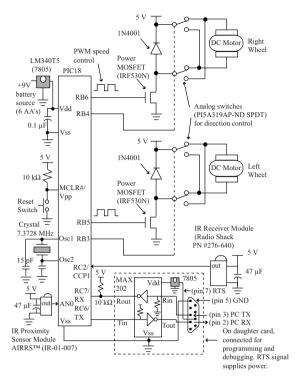

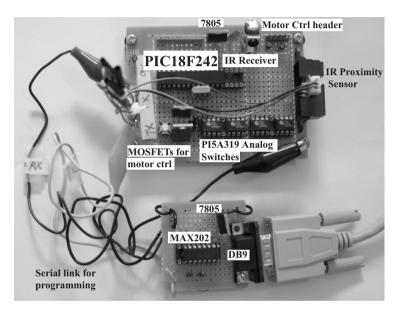

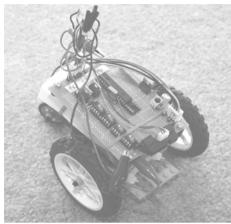

| 14.8 Design and Implementation of an Autonomous Robot | 494 |

| Summary                                               | 504 |

| Suggested Project Modifications                       | 505 |

| 15 Beyond the PIC18Fxx2                                                                       | 507 |

|-----------------------------------------------------------------------------------------------|-----|

| 15.1 Learning Objectives                                                                      | 507 |

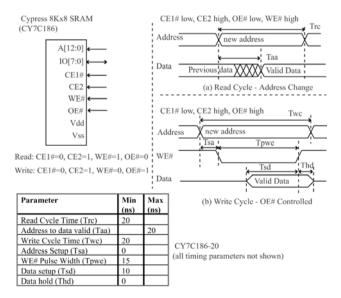

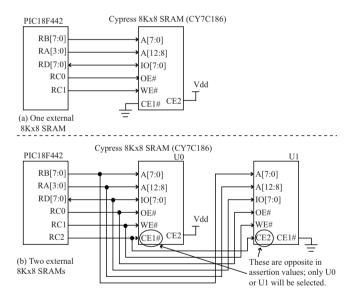

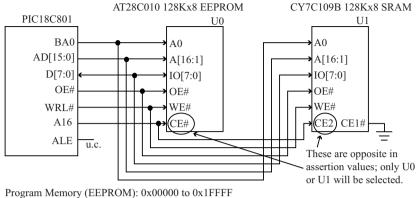

| 15.2 External Memory Interfacing                                                              | 508 |

| 15.3 Other PIC Family Members                                                                 | 513 |

| 15.4 Bus Arbitration in I <sup>2</sup> C                                                      | 516 |

| 15.5 The Controller Area Network (CAN)                                                        | 528 |

| 15.6 The Universal Serial Bus (USB)                                                           | 523 |

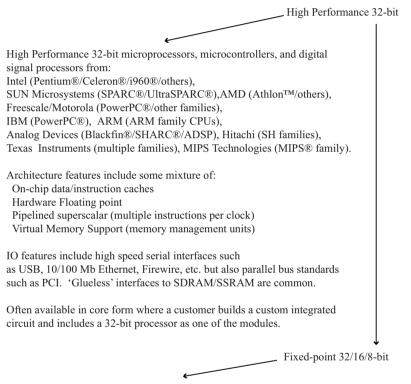

| 15.7 A Brief Survey of Non-PIC Microcontrollers                                               | 527 |

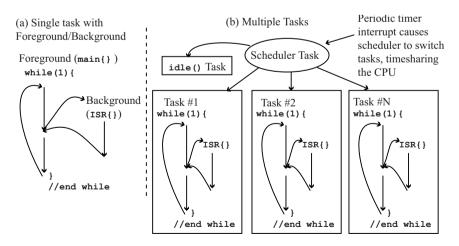

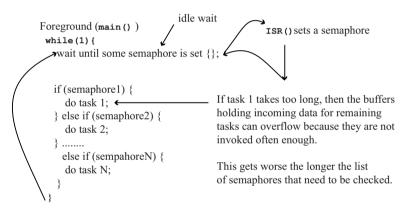

| 15.8 Real-Time Operating Systems                                                              | 531 |

| Summary                                                                                       | 533 |

| Suggested Survey Topics                                                                       | 534 |

| Appendix A PIC18Fxx2 Architecture, Instruction Set, Register Summary                          | 537 |

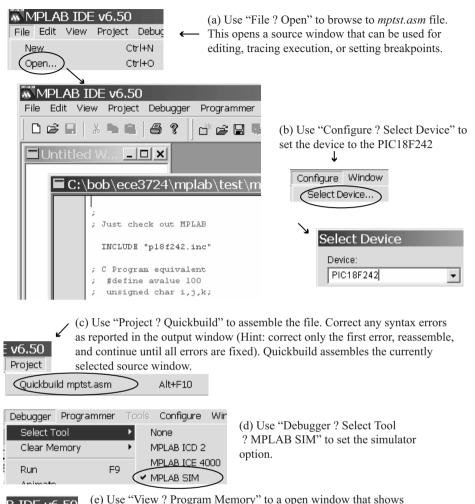

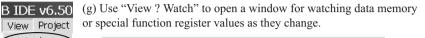

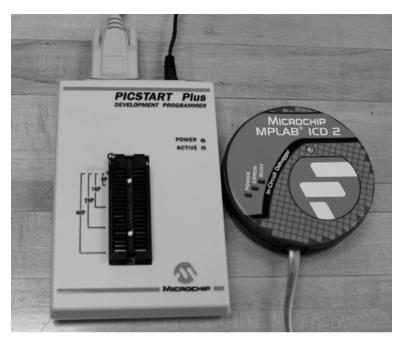

| Appendix B Microchip MPLAB Quickstart                                                         | 549 |

| Appendix C HI-TECH PICC-18 C Compiler Demo for the PIC18F242                                  | 553 |

| Appendix D Notes on the C Language                                                            | 557 |

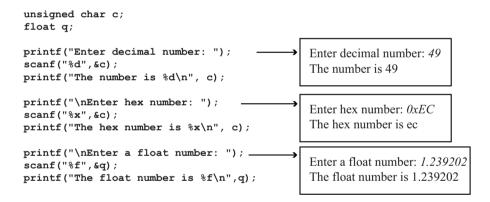

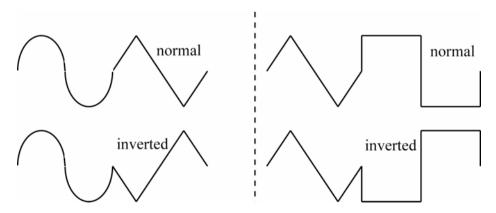

| D.1 Formatted IO (PRINTF, SCANF, SPRINTF, SSCANF)                                             | 557 |

| D.2 For C++ Programmers                                                                       | 559 |

| D.3 For New Programmers                                                                       | 560 |

| D.4 For Experienced C Programmers                                                             | 560 |

| Appendix E Suggested Laboratory Exercises                                                     | 563 |

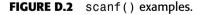

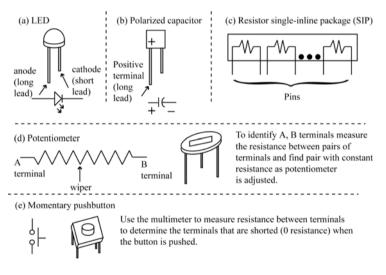

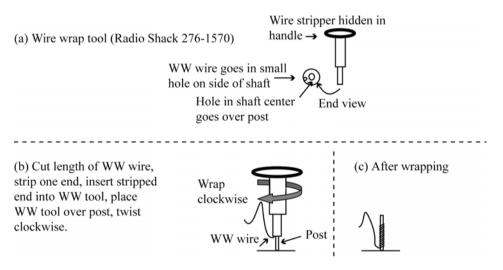

| E.1 Lab Setup                                                                                 | 563 |

| E.2 Experiment 1: A Stored Program Machine (Chapters 1, 2)                                    | 566 |

| E.3 Experiment 2: PIC18xx2 Introduction (Chapter 3)                                           | 567 |

| E.4 Experiment 3: Unsigned 8-Bit Operations (Chapter 4)                                       | 569 |

| E.5 Experiment 4: Extended Precision and Signed Operations (Chapter 5)                        | 572 |

| E.6 Experiment 5: Pointers and Subroutines (Chapter 6)                                        | 573 |

| E.7 Experiment 6: Hardware Startup (Chapter 8)                                                | 575 |

| E.8 Experiment 7: LED/Switch IO and Introduction to Asynchronous<br>Serial IO (Chapters 8, 9) | 578 |

| E.9 Experiment 8: Interrupts (Chapter 10)                                                     | 580 |

| E.10 Experiment 9: More Interrupts, the I <sup>2</sup> C Bus, and a Serial EEPROM (Chapter 11) | 583 |

|------------------------------------------------------------------------------------------------|-----|

| E.11 Experiment 10: Introduction to Data Conversion (Chapter 12)                               | 585 |

| E.12 Experiment 11: Timer Introduction and Waveform Generation                                 | 000 |

| (Chapters 10, 13)                                                                              | 587 |

| E.13 Experiment 12: Time Measurement and IR Waveform Decoding                                  |     |

| (Chapter 13)                                                                                   | 593 |

| E.14 Experiment 13: Audio Record/Playback (Chapter 14)                                         | 594 |

| E.15 Hardware Debugging Checklist                                                              | 595 |

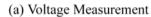

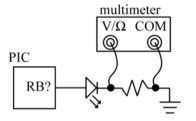

| E.16 Instrumentation and Prototyping Hints                                                     | 598 |

| Appendix F The Jolt/Colt Serial Bootloaders                                                    | 601 |

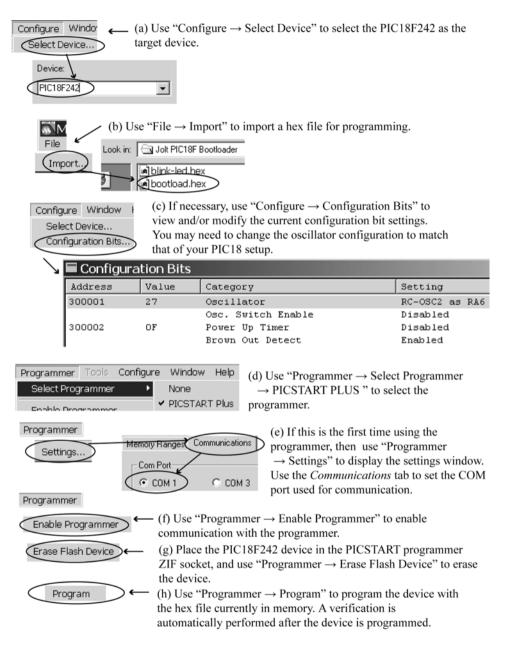

| F.1 Programming the Jolt/Colt Firmware                                                         | 601 |

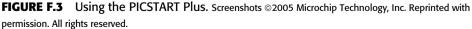

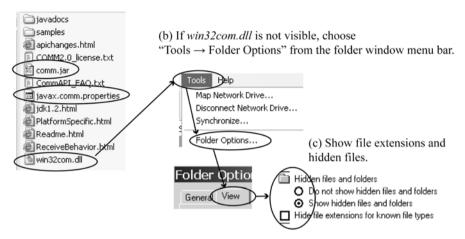

| F.2 Jolt Installation                                                                          | 605 |

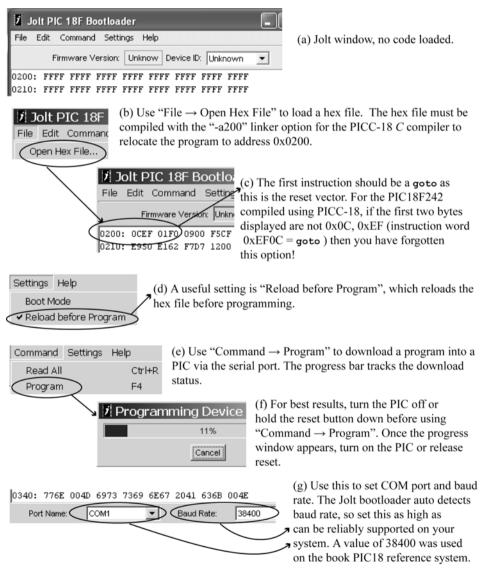

| F.3 Running Jolt                                                                               | 608 |

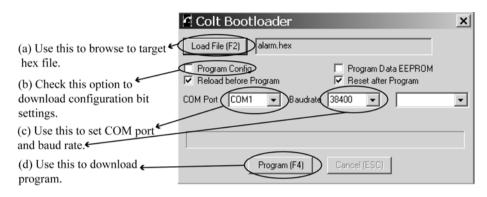

| F.4 Colt Bootloader Installation and Execution                                                 | 610 |

| Appendix G Circuits 001                                                                        | 613 |

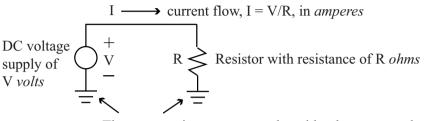

| G.1 Voltage, Current, Resistance                                                               | 613 |

| G.2 Capacitors                                                                                 | 618 |

| Appendix H References                                                                          | 621 |

| Appendix I Answers to Review Problems                                                          | 625 |

| I.1 Chapter 1                                                                                  | 625 |

| I.2 Chapter 2                                                                                  | 627 |

| I.3 Chapter 3                                                                                  | 629 |

| I.4 Chapter 4                                                                                  | 630 |

| I.5 Chapter 5                                                                                  | 631 |

| I.6 Chapter 6                                                                                  | 633 |

| I.7 Chapter 7                                                                                  | 638 |

| I.8 Chapter 8                                                                                  | 639 |

| I.9 Chapter 9                                                                                  | 643 |

| I.10 Chapter 10                                                                                | 644 |

| I.11 Chapter 11                                                                                | 646 |

| I.12 Chapter 12                                                                                | 647 |

| I.13 Chapter 13                 | 649 |

|---------------------------------|-----|

| Appendix J About the CD-ROM     | 655 |

| J.1 General System Requirements | 655 |

| Index                           | 657 |

## Acknowledgments

would like to thank the following individuals for their assistance in preparing this book:

- J.W. Bruce, for authoring Chapter 12 and for providing valuable feedback and suggestions on the rest of the book.

- Jane Moorhead, for being a partner in teaching this material to Mississippi State University (MSU) electrical engineering, computer engineering, computer science, and software engineering students.

ON THE CD

HI-TECH Software for providing the 120-day demo version of the PICC-18<sup>™</sup> C compiler that is included on this book's CD-ROM. I also want to thank Matt Luckman at HI-TECH Software for his efforts in putting that distribution together.

Donna Reese, for her careful proofreading of the book material.

This page intentionally left blank

# Preface

his book is intended as an introduction to microprocessors and microcontrollers for either the student or hobbyist. The book structure is:

Chapter 1: Review of digital logic concepts.

Chapter 2: Computer architecture fundamentals.

**Chapters 3 through 6:** Coverage of assembly language programming in a *C* language context using the PIC18Fxx2 family.

Chapter 7: Advanced assembly language programming structured around computer arithmetic topics.

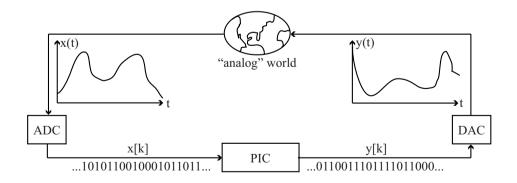

**Chapters 8 through 13:** Fundamental microcontroller interfacing topics such as parallel IO, asynchronous serial IO, synchronous serial IO (I<sup>2</sup>C and SPI), interrupt-driven IO, timers, analog-to-digital conversion, and digital-to-analog conversion.

**Chapter 14:** Presents three capstone projects involving topics from Chapters 8 through 13.

**Chapter 15:** Topics beyond the PIC18Fxx2 family, such as a survey of other microprocessor families, the CAN bus, and memory technologies.

#### USING THIS BOOK IN AN ACADEMIC ENVIRONMENT

At Mississippi State University, majors in Electrical Engineering (EE), Computer Engineering (CPE), Computer Science (CS), and Software Engineering (SE) take our first course in microprocessors. Previous to spring 2002, this course emphasized

X86 assembly language programming with the lab experience being 100-percent assembly language based and containing no hardware component. We found that students entering our senior design course who had the expectation of something "real" being built were unprepared for doing prototyping activities or for incorporating a microcontroller component into their designs. We did offer a course in microcontrollers, but it was an elective senior-level course and many students had not taken that course previous to senior design. In spring 2002, the Computer Engineering Steering committee reexamined our goals for the first course in microprocessors and the approach for this book was developed. This book is intended for use as a *first* course in microprocessors using the PIC18Fxx2 microcontroller with prerequisites of basic digital design and exposure to either C or C++ programming. The book begins with simple microprocessor architecture concepts, moves to assembly language programming in a C language context, and then covers fundamental hardware interfacing topics such as parallel IO, asynchronous serial IO, synchronous serial IO (I<sup>2</sup>C and SPI), interrupt-driven IO, timers, analog-to-digital conversion, and digital-to-analog conversion. Programming topics are discussed using both assembly language and C, while hardware interfacing examples uses C to keep code complexity low and improve clarity. The book's CD-ROM includes a 120-day demo version of the PICC-18 C compiler for the PIC18F242 from HI-TECH software. In addition to better preparing students for senior design, another goal of this book is to enable students to take courses in advanced embedded systems or computer architecture. As such, a broad coverage of software and hardware topics is included. The assembly language programming chapters emphasize the linkage between C language constructs and their assembly language equivalent so that students clearly understand the impact of C coding choices in terms of execution time and memory requirements. It is *not* a goal of this textbook to create students who are experts only in assembly language programming, with no understanding of high-level language programming techniques and limited hardware exposure. Most embedded software is written in C for portability and complexity reasons, which argues favorably for reduced emphasis on assembly language and increased emphasis on C. Embedded system hardware complexity is steadily increasing, which means a first course in microprocessors that reduces assembly language coverage (but does not eliminate it) in favor of hands-on experience with fundamental interfacing allows students to begin at a higher level in an advanced course in embedded systems. Hardware interface topics included in this book cover the fundamentals (parallel IO, serial IO, interrupts, timers, A/D, D/A) using devices that do not require extensive circuits knowledge because of the lack of a circuits course prerequisite. The microcontroller interfacing topics presented in this textbook are sufficient for providing a skill set that is extremely useful to a student in a senior design capstone course or in an advanced embedded system course.

Thus, the principle motivation for this book is that microcontroller knowledge has become essential for successful completion of senior capstone design courses. These capstone courses are receiving increased emphasis under ABET 2000 guidelines. This places increased pressure on Computer Engineering and Electrical Engineering programs to include significant exposure to embedded systems topics as early in the curriculum as possible. A second motivation for this book is that the recently released ACM/IEEE Computer Engineering model curriculum recommends 17 hours of embedded system topics as part of the Computer Engineering curriculum core, which is easily satisfied by a course containing the topics in this book. A third motivating factor is the increased pressure on colleges and universities to reduce hours in engineering curriculums; this book shows how a single course can replace separate courses in assembly language programming and basic microprocessor interfacing.

The course sequence used at Mississippi State University that this book fits into is:

- Basic digital design (Boolean algebra, combinational and sequential logic), which is required by EE, CPE, CS, and SE majors.

- Introduction to microprocessors (this book), which is required for EE, CPE, CS, and SE majors.

- Computer architecture as represented by the topic coverage of the Hennessy and Patterson textbook "Computer Organization & Design: The Hardware/ Software Interface." This includes reinforcement of the assembly language programming taught in the microprocessor course via a general-purpose instruction set architecture (e.g., the MIPS) along with coverage of traditional high-performance computer architecture topics (pipelined CPU design, cache strategies, parallel bus I/O). Required for CPE, CS, and SE majors.

- Advanced embedded systems covering topics such as (a) real-time operating systems, (b) internet appliances, (c) advanced interfaces such as USB, CAN, Ethernet, FireWire, and (d) programming in alternate embedded languages such as Java. Required for CPE majors.

Chapter 1 provides a broad review of digital logic fundamentals. Chapters 2 through 6 and 8 through 13 cover the core topics of assembly language programming and microcontroller interfacing. Chapter 14 contains three capstone projects that integrate the material of the previous chapters. Chapters 7 and 15 have

optional topics on advanced assembly language programming and microprocessor interfacing, which can be used to supplement the core material. Appendix E, "Suggested Laboratory Exercises," contains a sequence of 13 laboratory experiments that comprise an off-the-shelf lab experience: one experiment on fundamental computer architecture topics, four experiments on PIC18 assembly language, and eight hardware experiments. The hardware labs cover all major subsystems on the PIC18: A/D, timers, asynchronous serial interface, and the I<sup>2</sup>C interface. The hardware experiments are based on a protoboard/parts kit approach where the students incrementally build a PIC18F242 system that includes a serial EEPROM, an external 8-bit D/A, and a RS-232 port. A protoboard/part kits approach is used instead of a pre-assembled printed circuit board (PCB) for several important reasons:

- When handed a pre-assembled PCB, a student tends to view it as a monolithic element. A protoboard/parts kit approach forces a student to view each part individually and read datasheets to understand how parts connect to each other.

- Hardware debugging and prototyping skills are developed during the painful process of bringing the system to life. These hard-won lessons prove useful later when the student must do the same thing in a senior design context. This also provides students with the confidence that having done it one time they can do it again, this time outside of a fixed laboratory environment with guided instruction.

- A protoboard/parts kit approach gives the ultimate flexibility to modify experiments from semester to semester by simply changing a part or two; also when the inevitable part failures occur they are easily replaced.

In using this approach at Mississippi State University, I have seen a "Culture of Competence" develop in regard to microcontrollers and prototyping in general. Almost all senior design projects now routinely include a microcontroller component (not necessarily PIC-based). Students concentrate their efforts on design definition, development, and refinement instead of spending most of their time climbing the learning curve on prototyping and microcontroller usage.

This book's *C* examples on hardware interfacing strive for educational value first and optimization second. Subsystem configuration code uses named bit fields and individual bit field assignments in *C* examples instead of whole-register assignments to emphasize bit field roles within those registers. Register values for controlling baud rate, I<sup>2</sup>C bus speed, and periodic interrupt rates are hard-coded for the clock frequency of the reference PIC18F242 system instead of hiding the calculations within *C* macros or functions that compute a register value for a desired

rate. This is done intentionally so students can be assigned different values within the lab and homework exercises, forcing them to use the PIC18F242 datasheet formulas for computing new register values.

#### FOR THE HOBBYIST

This book assumes very little background, and thus is appropriate for readers with widely varying experience levels. It is suggested that you begin by examining the experiments in Appendix E and find the ones that interest you. Then, read the chapter that is referenced by the experiment. The suggested revisions for the capstone chapter projects (Chapter 14) are a good test of your knowledge once you have exhausted the experiments.

#### A Final Word

Writing this book has been a rewarding experience, and many people have helped (see the Acknowledgments section). It has been akin to building a stone wall; each day a little more is added, each section covering more distance, with the satisfaction of seeing it grow as time and effort is expended. However, this book's lifespan will be a fraction of that of a sturdily built stone wall. But that is the fun of engineering—it is constantly changing, so you are constantly learning. I hope that you have fun while learning about microprocessors and the PIC18Fxx2!

Bob Reese Starkville, Mississippi This page intentionally left blank

# Number System and Digital Logic Review

#### In This Chapter

- Binary Data

- Unsigned Number Conversion

- Binary and Hex Arithmetic

- Combinational Logic Functions

- Combinational Building Blocks

- Sequential Logic

- Sequential Building Blocks

- Encoding Character Data

This chapter reviews number systems, Boolean algebra, logic gates, combinational logic gates, combinational building blocks, sequential storage elements, and sequential building blocks.

#### **1.1 LEARNING OBJECTIVES**

After reading this chapter, you will be able to:

- Create a binary encoding for object classification.

- Convert unsigned decimal numbers to binary and hex representations, and vice versa.

- Identify NOT, OR, AND, NOR, NAND, and XOR logic functions and their symbols.

- Evaluate simple Boolean functions.

- Describe the operation of CMOS P and N transistors.

- Identify the CMOS transistor level implementations of simple logic gates.

- Compute clock period, frequency, and duty cycle given appropriate parameters.

- Identify common combinational building blocks.

- Identify common sequential building blocks.

- Translate a character string into ASCII encoded data, and vice versa.

Binary number system representation and arithmetic is fundamental to all computer system operation. Basic logic gates, CMOS transistor operation, and combinational/sequential building block knowledge will help your comprehension of the diagrams found in datasheets that describe microprocessor subsystem functionality. A solid grounding in these subjects ensures better understanding of the microprocessor topics that follow in later chapters.

#### **1.2 BINARY DATA**

Binary logic or digital logic is the basis for all computer systems built today. *Binary* means two, and many concepts can be represented by two values: true/false, hot/cold, on/off, 1/0, to name a few. A single binary datum whose values are "1" and "0" is referred to as a *bit*. Groups of bits are used to represent concepts that have more than two values. For example, to represent the concepts hot/warm/ cool/cold, two or more bits can be used as shown in Table 1.1

#### TABLE 1.1 Digital Encoding Examples

| 0 0 | 0 0 | 0001  |

|-----|-----|-------|

|     |     |       |

| 01  | 10  | 0010  |

| 10  | 11  | 0100  |

| 11  | 0 1 | 1000  |

|     | 10  | 10 11 |

To encode *n* objects, the minimum number of bits required is  $k = \lceil \log_2 n \rceil$ , where  $\rceil$  is the ceiling function that takes the nearest integer  $\ge \log_2 n$ . For the four

values in Table 1.1, the minimum number of bits required is  $\lceil \log_2(4) \rceil = 2$ . Both encoding A and encoding B use the minimum number of bits, but differ in how codes are assigned to the values. Encoding B uses a special encoding scheme known as *Gray* code, in which adjacent table entries only differ by at most one bit position. Encoding C uses more than the minimum number of bits; this encoding scheme is known as *one-hot encoding*, as each code only has a single bit that is a "1" value.

Encoding A uses *binary counting order*, which means that the code progresses in numerical counting order if the code is interpreted as a *binary number* (base 2). In an unsigned binary number, each bit is weighted by a power of two. The rightmost bit, or *least significant bit* (LSb), has a weight of  $2^0$ , with each successive bit weight increasing by a power of two as one moves from right to left. The leftmost bit, the *most significant bit* (MSb), has a weight of  $2^{n-1}$ , for *n* bits in the binary number. A lowercase "b" is purposefully used in the LSb and MSb acronyms; the use of an uppercase "B" in LSB and MSB acronyms is discussed later.

The formal term for a number's base is *radix*. If *r* is the radix, then a binary number has r = 2, a decimal number has r = 10, and a hexadecimal number has r = 16. In general, each digit of a number of radix *r* can take on the values 0 through r-1. The *least significant digit* (LSD) has a weight of  $r^0$ , with each successive digit increasing by a power of *r* as one moves from right to left. The leftmost digit, the *most significant digit* (MSD), has weight of  $r^{n-1}$ , where *n* is the number of digits in the number. For hexadecimal (hex) numbers, letters A through F represent the digits 10 through 15, respectively. Decimal, binary, and hexadecimal numbers are used exclusively in this book. If the base of the number (i.e., 0x3A), and "0b" for binary numbers (i.e., 0b01101000). No radix identifier is used for decimal numbers. Table 1.2 lists the binary and hex values for the decimal values 0 through 15. Note that 4 bits are required to encode these 16 values since  $2^4 = 16$ . The binary and hex values in Table 1.2 are given without radix identifiers.

| Decimal | Binary | Binary to Decimal                                   | He | x Hex to Decima   |

|---------|--------|-----------------------------------------------------|----|-------------------|

| 0       | 0000   | $0^{*}2^{3} + 0^{*}2^{2} + 0^{*}2^{1} + 0^{*}2^{0}$ | 0  | 0*16 <sup>0</sup> |

| 1       | 0001   | $0^{*}2^{3} + 0^{*}2^{2} + 0^{*}2^{1} + 1^{*}2^{0}$ | 1  | 1*16 <sup>0</sup> |

| 2       | 0010   | $0^{*}2^{3} + 0^{*}2^{2} + 1^{*}2^{1} + 0^{*}2^{0}$ | 2  | 2*16 <sup>0</sup> |

| 3       | 0011   | $0^{*}2^{3} + 0^{*}2^{2} + 1^{*}2^{1} + 1^{*}2^{0}$ | 3  | 3*16 <sup>0</sup> |

| 4       | 0100   | $0^{*}2^{3} + 1^{*}2^{2} + 0^{*}2^{1} + 0^{*}2^{0}$ | 4  | 4*16 <sup>0</sup> |

| 5       | 0101   | $0^{*}2^{3} + 1^{*}2^{2} + 0^{*}2^{1} + 1^{*}2^{0}$ | 5  | 5*16 <sup>0</sup> |

| 6       | 0110   | $0^{*}2^{3} + 1^{*}2^{2} + 1^{*}2^{1} + 0^{*}2^{0}$ | 6  | 6*16 <sup>0</sup> |

|         |        |                                                     |    |                   |

**TABLE 1.2** Binary Encoding for Decimal Numbers 0-15

| 7  | 0111 | $0^{*}2^{3} + 1^{*}2^{2} + 1^{*}2^{1} + 1^{*}2^{0}$ | 7 | 7*16 <sup>0</sup>  |

|----|------|-----------------------------------------------------|---|--------------------|

| 8  | 1000 | $1^{*}2^{3} + 0^{*}2^{2} + 0^{*}2^{1} + 0^{*}2^{0}$ | 8 | 8*16 <sup>0</sup>  |

| 9  | 1001 | $1^{*}2^{3} + 0^{*}2^{2} + 0^{*}2^{1} + 1^{*}2^{0}$ | 9 | 9*16 <sup>0</sup>  |

| 10 | 1010 | $1^{*}2^{3} + 0^{*}2^{2} + 1^{*}2^{1} + 0^{*}2^{0}$ | Α | 10*16 <sup>0</sup> |

| 11 | 1011 | $1^{*}2^{3} + 0^{*}2^{2} + 1^{*}2^{1} + 1^{*}2^{0}$ | В | 11*16 <sup>0</sup> |

| 12 | 1100 | $1^{*}2^{3} + 1^{*}2^{2} + 0^{*}2^{1} + 0^{*}2^{0}$ | С | 12*16 <sup>0</sup> |

| 13 | 1101 | $1^{*}2^{3} + 1^{*}2^{2} + 0^{*}2^{1} + 1^{*}2^{0}$ | D | 13*16 <sup>0</sup> |

| 14 | 1110 | $1^{*}2^{3} + 1^{*}2^{2} + 1^{*}2^{1} + 0^{*}2^{0}$ | Е | 14*16 <sup>0</sup> |

| 15 | 1111 | $1^{*}2^{3} + 1^{*}2^{2} + 1^{*}2^{1} + 1^{*}2^{0}$ | F | 15*16 <sup>0</sup> |

|    |      |                                                     |   |                    |

A binary number of N bits can represent the unsigned decimal values of 0 to  $2^{N}-1$ . A common size for binary data is a group of 8 bits, referred to as a *byte*. A byte can represent the unsigned decimal range of 0 to 255 (0x00 to 0xFF in hex). Groups of bytes are often used to represent larger numbers; this topic is explored in Chapter 5, "Extended Precision and Signed Operations." Common powers of two are given in Table 1.3. Powers of two that are evenly divisible by  $2^{10}$  can be referred to by the suffixes K (Kilo,  $2^{10}$ ), M (Mega,  $2^{20}$ ), and G (Giga,  $2^{30}$ ). Thus, the value of 4096 can be written in the abbreviated form of 4 K (4 x 1 K =  $2^2$  x  $2^{10} = 2^{12}$ ).

| Power                 | Decimal | Hex   | Power                  | Decimal       | Hex         |

|-----------------------|---------|-------|------------------------|---------------|-------------|

| 2 <sup>0</sup>        | 1       | 0x1   | (K)2 <sup>10</sup>     | 1024          | 0x400       |

| 2 <sup>1</sup>        | 2       | 0x2   | 211                    | 2048          | 0x800       |

| <b>2</b> <sup>2</sup> | 4       | 0x4   | <b>2</b> <sup>12</sup> | 4096          | 0x1000      |

| 2 <sup>3</sup>        | 8       | 0x8   | 2 <sup>13</sup>        | 8192          | 0x2000      |

| 2 <sup>4</sup>        | 16      | 0x10  | 2 <sup>14</sup>        | 16384         | 0x4000      |

| 2 <sup>5</sup>        | 32      | 0x20  | 2 <sup>15</sup>        | 32768         | 0x8000      |

| 2 <sup>6</sup>        | 64      | 0x40  | 2 <sup>16</sup>        | 65536         | 0x10000     |

| <b>2</b> <sup>7</sup> | 128     | 0x80  | (M)2 <sup>20</sup>     | 1,048,576     | 0x100000    |

| 2 <sup>8</sup>        | 256     | 0x100 | (G)2 <sup>30</sup>     | 1,073,741,824 | 0x40000000  |

| 2 <sup>9</sup>        | 512     | 0x200 | 2 <sup>32</sup>        | 4,294,967,296 | 0x100000000 |

|                       |         |       |                        |               |             |

| TABLE 1.3 | Common Powers of 2 |

|-----------|--------------------|

|           |                    |

Sample Question: What is the largest unsigned decimal number that can be represented using a binary number with 16 bits?

Answer: From Table 1.3, we see that  $2^{16} = 65536$ , so  $2^{16}-1 = 65535$ .

#### **1.3 UNSIGNED NUMBER CONVERSION**

To convert a number of any radix to decimal, simply multiply each digit by its corresponding weight and sum the result. The example that follows shows binary-todecimal, and hex-to-decimal conversion:

| (binary to decimal) 0b0101 0010 | $= 0^{*}2^{7} + 1^{*}2^{6} + 0^{*}2^{5} + 1^{*}2^{4} + 0^{*}2^{3} +$ |

|---------------------------------|----------------------------------------------------------------------|

|                                 | $0^{2^{2}+1^{2^{1}}+0^{2^{0}}}$                                      |

|                                 | = 0 + 64 + 0 + 16 + 0 + 0 + 2 + 0 = 82                               |

| (hex to decimal) 0x52           | $= 5^* 16^1 + 2^* 16^0 = 80 + 2 = 82.$                               |

To convert a decimal number to a different radix, perform successive division of the decimal number by the radix; at each step the remainder is a digit in the converted number, and the quotient is the starting value for the next step. The successive division ends when the quotient becomes less than the radix. The digits of the converted number are determined rightmost to leftmost; with the last quotient being the leftmost digit of the converted number. The following sample problem illustrates the successive division algorithm.

#### Sample Question: Convert 435 to hex

| Answer:       |                                                  |

|---------------|--------------------------------------------------|

| Step 1:       | 435/16 = 27, remainder = 3 (rightmost digit).    |

| Step 2:       | 27/16 = 1, remainder $= 11 = 0$ xB (next digit). |

| Step 3:       | 1 < 16, so leftmost digit = 1.                   |

| Final answer: | 435 = 0x1B3.                                     |

To check your work, perform the reverse conversion:  $0x1B3 = 1 * 16^2 + 11 * 16^1 + 3 * 16^0 = 1 * 256 + 11 * 16 + 3 * 1 = 256 + 176 + 3 = 435.$

#### Hex to Binary, Binary to Hex

Hex can be viewed as a shorthand notation for binary. A quick method for performing binary-to-hex conversion is to convert each group of four binary digits (starting with the rightmost digit) to one hex digit. If the last (leftmost) group of binary digits does not contain 4 bits, then pad with leading zeros to reach four digits. Converting hex to binary is the reverse procedure of replacing each hex digit with four binary digits. The easiest way to perform decimal-to-binary conversion is to first convert to hex, and then convert the hex number to binary. This involves less division operations, and hence less chance for careless error. Similarly, binary-todecimal conversion is best done by converting the binary number to a hex value, and then converting the hex number to decimal. The following examples illustrate binary-to-hex, hex-to-binary, and decimal-to-binary conversion.

#### Sample Question: Convert 0b010110 to hex.

*Answer:* Starting with the rightmost digit, form groups of four: 01 0110. The leftmost group has only two digits, so pad this group with zeros as: 0001 0110. Now convert each group of four digits to hex digits (see Table 1.3): 0b 0001 0110 = 0x 16.

#### Sample Question: Convert 0xF3C to binary.

*Answer:* Replace each hex digit with its binary equivalent: 0x F3C = 0b 1111 0011 1100

#### Sample Question: Convert 243 to binary.

Answer: First, convert 243 to hex: Step 1: 243/16 = 15, remainder 3 (rightmost digit) Step 2: 15 < 16, so leftmost digit is 0xF(15). Hex result is 0xF3243 = 0xF3 = 0b 1111 0011 (final answer, in binary) Check: 0xF3 = 15 \* 16 + 3 = 240 + 3 = 243.

#### **1.4 BINARY AND HEX ARITHMETIC**

Addition, subtraction, and shift operations are implemented in some form in most digital systems. The fundamentals of these operations are reviewed in this section, and revisited in Chapters 3 and 4 when discussing basic computer operations.

#### **Binary and Hex Addition**

Addition of two numbers, i + j, in any base is accomplished by starting with the rightmost digit and adding each digit of *i* to each digit of *j*, moving right to left. If the digit sum is less than the radix, the result digit is the sum and a carry of 0 is used in the next digit addition. If the sum of the digits is greater than or equal to the radix, a carry of 1 is added to the next digit sum, and the result digit is computed by subtracting *r* from the digit sum. For binary addition, these rules can be stated as:

- 0+0=0, carry = 0

- 0+1 = 1, carry = 0

- 1+0 = 1, carry = 0

- 1+1 = 0, carry = 1

Figure 1.1 shows a digit-by-digit addition for the numbers 0b110 + 0b011. Note that the result is 0b001 with a carry out of the most significant digit of "1". A carry out of the most significant digit indicates that the sum produced *unsigned overflow*; the result could not fit in the number of available digits. A carry out of the most significant digit is an unsigned error indicator if the numbers represent unsigned integers. In this case, the sum 0b110 + 0b011 is 6 + 3 with the correct answer being 9. However, the largest unsigned integer that can be specified in 3 bits is  $2^3-1$ , or 7. The value of 9 is too large to be represented in 3 bits, and thus the result is incorrect from an arithmetic perspective, but is correct by the rules of binary addition. This is known as the limited precision problem; only increasing the number of bits used for binary encoding can increase the number range. We study this problem and the consequences of using more or less bits for number representation in more detail in Chapter 5.

FIGURE 1.1 Binary addition example.

#### Sample Question: Compute 0x1A3 + 0x36F.

Answer: A digit-by-digit addition for the operation 0x1A3 + 0x36F is as follows. The rightmost result digit is formed by adding 0x3 (3) + 0xF (15) = 18. Note the digit sum is  $\geq$  than 16, so a carry of 1 is produced and the rightmost result digit is computed by subtracting the radix, or 18 - 16 = 2 = 0x2. The middle digit sum is then 0xA (10) + 0x6 (6) + 1 (carry) = 17. This digit sum is  $\geq$  than 16, so this produces a carry of 1 with the middle digit computed as 17 - 16 = 1 = 0x1. The leftmost digit sum is 0x1 + 0x3 + 0x1 (carry) = 0x5. The result is then 0x1A3 + 0x36F = 0x512. Converting each number to decimal before summing, or 419 + 879 = 1298, checks this regult. Verifying that 0x36F - 0x512 = 0x1A3 also checks this result, but this requires reading the next section on subtraction!

#### **Binary and Hex Subtraction**

Subtraction of two numbers, i - j, in any base is accomplished by starting with the rightmost digit, and subtracting each digit of j from each digit of i, moving right to left. If the i digit is greater or equal to the j digit, then the result digit is the subtraction i - j, with a borrow of 0 used in the next digit subtraction. If the i digit is less than the j digit, then a borrow of 1 is used in the next digit subtraction, and the result digit is formed by i + r - j (the current i digit is increased by a weight of r). For binary subtraction, these rules can be stated as:

- 0 0 = 0, borrow = 0

- 0 1 = 1, borrow = 1

- 1 0 = 1, borrow = 0

- 1 1 = 0, borrow = 0

Figure 1.2 shows a digit-by-digit subtraction for the value 0b010 - 0b101. This operation produces a result of 0b101, and a borrow out of the most significant digit of 1. If interpreted as unsigned numbers, the operation is 2 - 5 = 5, which is incorrect. A borrow out of the most significant digit of 1 indicates an *unsigned underflow*; the correct result is a number less than zero. But in unsigned numbers, there is no number less than zero, so the result is incorrect in an arithmetic sense (the operation is perfectly valid, however). A binary representation for *signed integers* is needed to interpret the binary result correctly; this topic is saved for Chapter 5.

$$-1 - 1 + 2 - 1 + 2$$

$$- \frac{0}{1} + 2 - 1 + 2$$

$$- \frac{0}{1} + 2 - 1 + 2$$

$$- \frac{0}{1} - \frac{1}{0} + 2$$

Borrow

FIGURE 1.2 Binary subtraction example.

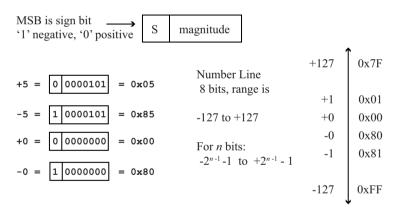

The subtraction A - B can also be performed by the operation A + ~B + 1, where the operation ~B is called the *one's complement* of B and is formed by taking the complement of each bit of B. As an example, consider the previous operation of 0b010 - 0b101. The one's complement of 0b101 is 0b010. The subtraction can be rewritten as:

$$A + \sim B + 1 = 0b010 + (0b010 + 0b001) = 0b010 + 0b011 = 0b101$$

This is the same result obtained when binary subtraction rules were used. The value  $\sim B + 1$  is called the *two's complement* of B, and this is discussed in more detail in Chapter 5, "Extended Precision and Signed Operations," when signed integer representation is covered.

#### Sample Question: Compute 0xA02 - 0x5C4.

Answer: A digit-by-digit hex subtraction for the operation 0xA02 - 0x5C4 is as follows. The rightmost subtraction of 0x2 - 0x4 requires a borrow from the next digit, so the rightmost digit calculation becomes 2 + 16 - 4 = 14 = 0xE. The middle digit calculation becomes 0x0 - 0xC - 0x1 (borrow). This requires a borrow from the next (leftmost) digit, so this calculation becomes:

16 + 0 - 12 - 1 = 3 = 0x3

The leftmost digit calculation is:

$$0xA - 0x5 - 0x1$$

(borrow) =  $10 - 5 - 1 = 4 = 0x4$

Thus, the final result is 0xA02 - 0x5C4 = 0x43E. As always, this result can be checked by verifying that 0x5C4 + 0x43E = 0xA02 (and yes, it is correct!).

#### **Shift Operations**

A right shift of a binary value moves all of the bits to the right by one position, and shifts a new bit value into the MSb. If the new shift value is a "0", this is equivalent to dividing the binary value by two. For example, using a "0" value for the bit shifted into the MSb, the binary value 0b1100 (12) shifted to the right by one position is 0b0110 (6). If this value is shifted to the right once more, the new value is 0b0011 (3). In this book, operators from the *C* language are used for expressing numerical operations. The *C* language operator for a right shift is >>, where A >> 1 reads "A shifted to the right by one bit."

A left shift of an unsigned binary value moves all of the bits to the left by one position, and shifts a new bit value into the LSb. If the new bit shifted in is a "0", this is equivalent to multiplying the binary value by two. For example, using a "0" value for the bit shifted into the LSb, the binary value 0b0101 (5) shifted to the left by one position is 0b1010 (10). If this value is shifted to the left once more, the new value is 0b0100 (4). The value 4 is not 10\*2; the correct result should be 20. However, the value 20 cannot fit in 4 bits; the largest unsigned value represented in 4 bits is  $2^4 - 1 = 15$ . In this case, the bit shifted out of the MSb is a "1"; when this happens, unsigned overflow occurs for the shift operation and the new value is incorrect in

an arithmetic sense. The *C* language operator for a left shift is <<, where A<<1 reads "A shifted to the left by one bit". Figure 1.3 gives additional examples of left and right shift operations.

Shift inShift in

$$0$$

$1$  $1$  $0$  $1$  $1$  $1$  $1$  $0$  $1$  $1$  $0$  $1$  $1$  $0$  $1$  $1$  $0$  $1$  $1$  $0$  $1$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $1$  $0$  $1$  $0$  $1$  $0$  $1$  $1$  $0$

FIGURE 1.3 Shift operation examples.

If an *n*-bit value is shifted to the left or right *n* times, with "0" used as the shiftin value, the result is zero, as all bits become "0". When shifting a hex value, it is best to convert the hex number to binary, perform the shift, and then convert the binary number back to hex.

Sample Question: What is the new value of 0xA7 >> 2 assuming the MSb is filled with a "0"?

Answer: The value  $0xA7 = 0b1010\ 0111$ , so 0xA7 >> 1 = 0b01010011. Shifting this value to the right by one more gives 0b01010011 >> 1 = 0b00101001 = 0x29. Therefore, 0xA7 >> 2 = 0x29.

#### **1.5 COMBINATIONAL LOGIC FUNCTIONS**

*Boolean algebra* defines properties and laws between variables that are binaryvalued. The basic operations of Boolean algebra are NOT, OR, and AND whose definitions are:

**NOT**(A): Is "1" if A = 0; NOT(A) is "0" if A = 1 (the output is said to be the *complement* or *inverse* of the input).

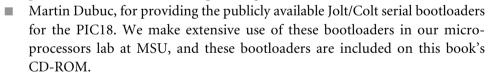

AND(A1, A2,...An): Is "1" only if all inputs A1 through An have value = 1. OR (A1, A2, ...An): Is "1" if any input A1 through An has value "1". The *C* language operators for bitwise complement ("~"), AND ("&"), OR ("|") are used in this book for logic operations. Thus, NOT(A) =  $\sim$ A, AND(A,B) = A & B, and OR(A,B) = A | B where the Boolean variables have values of either "0" or "1". Logic operations are also defined by *truth tables* and shape distinctive symbols. A truth table has all input combinations listed in binary counting order on the left side, with the output value given on the right side of the table. Figure 1.4 lists the two-input truth tables and shape distinctive symbols for the NOT, AND, OR, NAND, NOR, and XOR (exclusive-OR) logic functions.

FIGURE 1.4 Truth table, logic symbols for basic two-input logic gates.

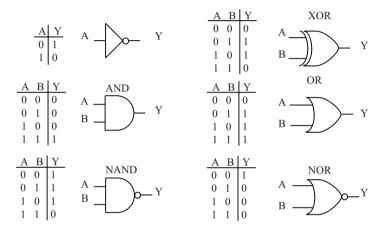

A NAND function is an AND function whose output is complemented; similarly, a NOR function is an OR function whose output is complemented. An XOR function is defined by the truth table shown in Figure 1.4, or can be expressed using NOT, AND, OR operators as shown in Equation 1.1. The *C* language operator for XOR is  $^$ , thus XOR(A,B) = A  $^$  B. Logically stated, XOR(A,B) is "1" if A is not equal to B, and "0" otherwise.

$$Y = (A \& (\sim B)) | ((\sim A) \& B)$$

(Exclusive OR function) (1.1)

The shape distinctive symbol for a Boolean logic function is also referred to as the *logic gate* for the Boolean operation. A network of logic gates is an alternative representation of a Boolean equation. Figure 1.5 shows the Boolean equation of the XOR function drawn as a logic network using two-input gates.

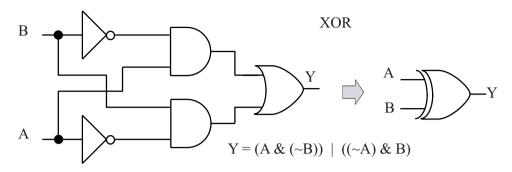

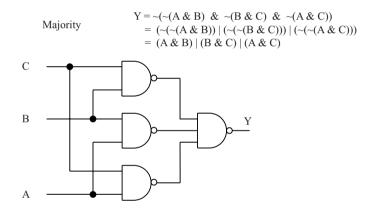

Figure 1.6 gives the AND/OR network, Boolean equation, and truth table for a three-input majority function; so named because the output is a "1" only when a majority of the inputs are a "1".

FIGURE 1.5 AND/OR logic network for XOR function.

FIGURE 1.6 AND/OR logic network for the three-input majority function.

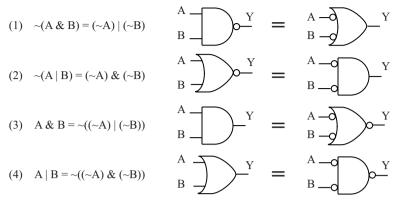

An important law relating AND/OR/NOT relationships is known as *DeMorgan's Law*, with its forms shown in Figure 1.7. A "circle" or "bubble" on a gate input means that input is complemented. Note that a NAND function can be replaced by an OR function with complemented inputs (Form 1); while a NOR function can be replaced by an AND function with complemented inputs (Form 2). Forms 1 and 2 of DeMorgan's Law can be validated by comparing the truth tables of the left and right hand sides, while forms 3 and 4 follow from substitution of forms 1 and 2.

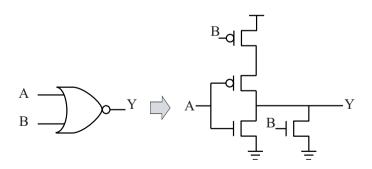

DeMorgan's law can be used to replace all of the AND/OR gates of Figure 1.6 with NAND gates as shown as in Figure 1.8. This is important as the physical implementation of a NAND gate using Complementary Metal Oxide Semiconductor (CMOS) transistors is faster and has fewer transistors than either an AND gate or an OR gate.

FIGURE 1.7 DeMorgan's Law.

**FIGURE 1.8** NAND/NAND logic network for a three-input majority function.

#### **Logic Gate CMOS Implementations**

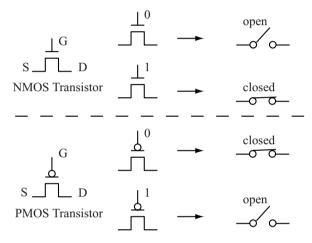

CMOS transistors are the most common implementation method used today for logic gates, which form the building blocks for all digital computation methods. We review the basics of CMOS transistor operation here and revisit the topic in Chapter 8 when discussing computer input/output. The "C" in CMOS stands for *complementary*, which refers to the fact that there are two types of MOS transistors, N and P, whose operation is complementary to each other. Each MOS transistor type has three terminals: *Gate* (g), *Source* (s), and *Drain* (d). For our purposes, we will view a MOS transistor as an ideal switch whose operation is controlled by the gate terminal. The switch is either closed (connection exists between source and drain, so current flows between source and drain) or open (no connection between source)

and drain, no current flow between source and drain). An N-type transistor is open when the gate has a logic "0", and closed when the gate has a logic "1". A P-type transistor has complementary operation; a "1" on the gate opens the switch, a "0" closes the switch. A logic "1" is physically represented by the power supply voltage of the logic gate, or *Vdd*. The power supply voltage used for a CMOS logic gate can vary widely, from 5 V (Volts) down to approximately 1.2 V. A logic "0" is physically represented by the system ground, or *Gnd*, which has a voltage value of 0 V. Figure 1.9 illustrates P and N transistor operation.

FIGURE 1.9 CMOS transistor operation.

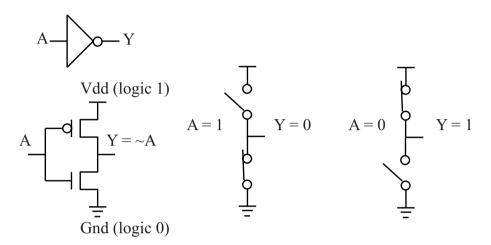

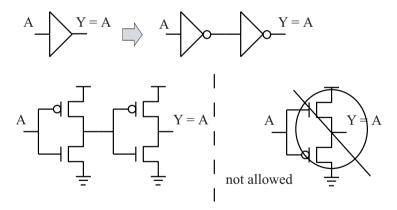

Multiple CMOS transistors can be connected to form logic gates. Figure 1.10 shows the simplest CMOS logic gate, which is the NOT function, or *inverter*. When the input value is "0", the upper switch (the P transistor) is closed, while the lower switch (the N transistor) is open. This connects the output to Vdd, forcing the output to a "1". When the input value is "1", the upper switch is open, while the lower switch is closed. This connects the output to Gnd, forcing the output to a "0". Thus, for an input of "0" the output is "1"; for an input of "1" the output is a "0", which implements the NOT function.

Note that a buffer function Y = A is formed if two inverters are tied back to back as shown in Figure 1.11. It would seem that a better way to build a buffer is to switch the positions of the N and P transistors of the inverter; thus implementing the buffer with only two transistors instead of four. However, for physical reasons best left to an electronics book, a P transistor is always used to pass a "1" value, while an N transistor is always used to pass a "0" value. Thus, in digital logic, a P transistor is never tied to ground, and an N transistor is never tied to Vdd, so the two-transistor buffer shown in Figure 1.11 is illegal. A noninverting CMOS logic function always takes two stages of inverting logic.

FIGURE 1.10 CMOS inverter operation.

FIGURE 1.11 CMOS buffer.

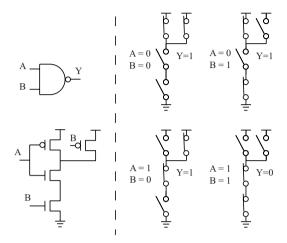

Figure 1.12 shows the transistor configuration and operation of a two-input CMOS NAND gate. Note that the output is connected to ground (both bottom transistors are closed) only when both inputs are a "1" value. Also observe that no combination of inputs provides a direct path between Vdd and Gnd; this would cause a *short* (low resistance path) between Vdd and Gnd resulting in excessive

current flow. The four-transistor configuration for a CMOS NOR gate is left as an exercise for the review problems.

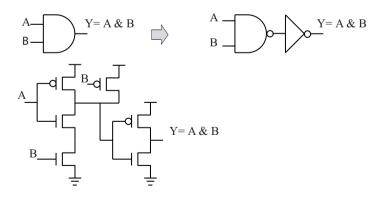

Figure 1.13 shows that a CMOS AND gate is actually built from a NAND gate followed by an inverter. Similarly, a CMOS OR gate is built from a NOR gate followed by an inverter. This clearly shows why replacing AND/OR logic with NAND gates via DeMorgan's Law is a good idea. The resulting circuit requires less transistors, meaning it is faster, consumes less power, and is cheaper to manufacture!

FIGURE 1.13 A CMOS AND gate.

## **1.6 COMBINATIONAL BUILDING BLOCKS**

Building logic circuits on a gate-by-gate basis is an exercise that can be quite fun, once. After that, one should look for shortcuts that reduce design time for complex circuits. One method for building complex combinational circuits quickly is to use combinational *building blocks*. The following sections describe some commonly used combinational building blocks; this list is by no means exhaustive. It should not be surprising that some of these building blocks (the adder and shifter) implement the arithmetic operations discussed earlier.

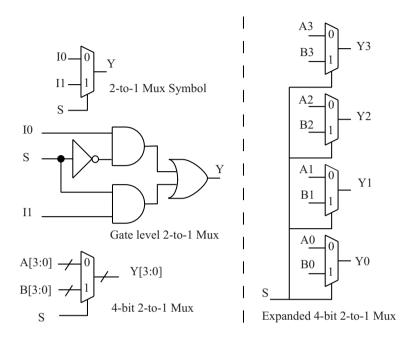

#### **The Multiplexer**

A K-to-1 Multiplexer (or mux) steers one of K inputs to the output. The most common mux type is a 2-to-1 mux (two inputs, one output). A select control input S chooses the input that is passed to the output. The operation of 2-to-1 mux is written in C code as:

if (S) Y = A; else Y = B;

This *C* code description of a mux reads as "if S is non-zero, output Y is equal to A, else output Y is equal to B". The Boolean equation for 2-to-1 1-bit mux is given in Equation 1.2.

$$Y = (S \& I1) | (~S \& I0)$$

(1.2)

Figure 1.14 shows the gate equivalent for a 1-bit 2-to-1 mux and how a 4-bit 2-to-1 mux is built from four of these 1-bit building blocks. The 4-bit mux symbol in Figure 1.15 uses a *bus* labeling notation for the A and B inputs. In this context, a *bus* is simply a collection of parallel wires; a bus named A with N wires is designated as A[N-1:0]. The LSb and MSb of bus A are A[0] and A[N-1], respectively. If N = 8, the entire bus A is labeled as A[7:0], the LSb is A[0], and the MSb is A[7].

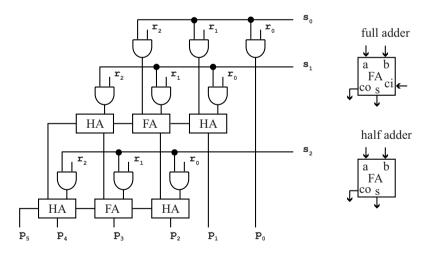

#### **The Adder**

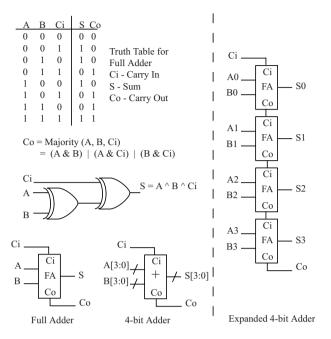

The adder takes two N-bit inputs (A, B) and computes the N-bit sum (A + B). Most adders have a carry-in bit input for the LSb addition, and a carry-out bit output from the MSb addition. A *full adder* logic circuit that adds A + B + Ci (carry-in) and produces sum (S) and carry-out (Co) is a 1-bit building block of most adder circuits. Figure 1.15 shows the truth table, Boolean equations, and logic network for a full adder. The same figure shows how to build a 4-bit *ripple-carry* adder from four 1-bit full adders; the term *ripple-carry* is used because the carry ripples

from the rightmost bit to the leftmost bit. There are many other ways to build an adder; this is the simplest form of a binary adder.

FIGURE 1.14 One-bit 2-to-1 mux, 4-bit 2-to-1 mux.

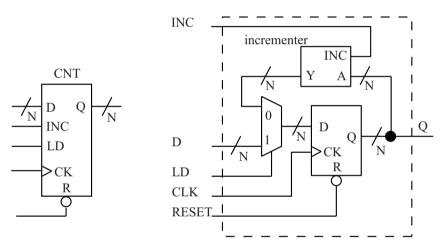

#### **The Incrementer**

The operation of an incrementer is described by the following *C* code:

if (INC) Y = A+1; else Y = A;

The INC (increment) input is a single bit input that determines if the N-bit output is A + 1 or just A. An incrementer can be built from an adder by connecting all bits of one N-bit input to zero, and using the carry-in input as the INC input. This computes the sum Y = A + 0 + 1 when INC = 1 or the value Y = A + 0 + 0 when INC = 0. There are more efficient methods in terms of logic gate count to implement an incrementer, but this illustrates the flexibility of combinational building blocks in implementing different functions.

FIGURE 1.15 One-bit adder, 4-bit ripple adder.

#### **The Shifter**

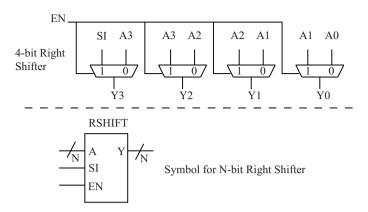

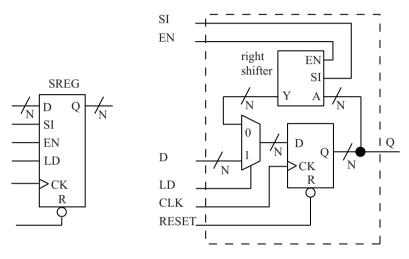

There are many varieties of shifter combinational building blocks. The simplest type shifts by only one position, and in a fixed direction (either left or right). More complex types can shift multiple positions, and in either direction. Figure 1.16 shows the logic symbol for an N-bit right shifter, and the internal details of a 4-bit right shifter. When EN = 1, then Y = A >> 1 with the SI input providing the input bit for the MSb. When EN = 0, then Y = A, and the SI input has no effect. This is another example of simple combinational building blocks (2-to-1 muxes) being used to build a more complex combinational building block.

#### Memory

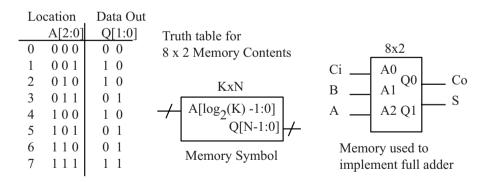

A KxN memory device has K locations, with each location containing N bits. Thus, a 16x1 memory has 16 locations, with each location containing 1 bit. The *address* inputs specify the location whose contents appear on the data output. The number of bits required for the address is  $\lceil \log_2 K \rceil$ , a relationship seen previously as the address bits are used to uniquely specify 1 of K locations. The output databus has N bits as it is used to output the contents of a memory location. Following these rules, a 16x1 memory has  $\lceil \log_2 16 \rceil = 4$  address inputs, and one data output. The

FIGURE 1.16 N-bit right shift symbol and 4-bit right shift details.

idealistic view of memory presented here assumes a memory type with only these inputs and outputs, with memory contents loaded by some external means not discussed here. The most common usage of memory is to store data, but it can also be used to implement logic functions. Figure 1.17 shows an 8x2 memory used to implement the sum and carry-out equations of the full adder. The full adder inputs are connected to the 3-bit address bus as A = ADDR2, B = ADDR1, and Ci = ADDR0. The 2-bit data output bus provides the outputs as Co = Q0 and S = Q1.

FIGURE 1.17 Full adder implemented by an 8x2 memory.

Sample Question: How many address and data lines does a 4Kx16 memory have? Answer: The number of address inputs is  $\lceil \log_2 4K \rceil = \lceil \log_2 2^{2*} 2^{10} \rceil = \lceil \log_2 2^{12} \rceil = 12$ . The number of data outputs is 16.

# **1.7 SEQUENTIAL LOGIC**

The output of a combinational logic block is always uniquely defined by its current inputs. In contrast, the output of a *sequential* logic element is defined by its current inputs and also its *current state*, a value that is internal to the sequential logic element. A sequential logic element is a form of a memory device in that it retains internal state information between operations. In discussing sequential logic, the terms *asserted*, *negated*, *high-true*, and *low-true* are used in reference to inputs. When an input is *asserted*, it is said to contain a TRUE value; a *negated* input contains a FALSE value. A *high-true* input has a high voltage level for TRUE, and a low voltage level for FALSE. A *low-true* input has a low voltage level for TRUE, and a high voltage level for FALSE. The symbol for a sequential logic element uses a bubble on an input to indicate low-true.

### **The Clock Signal**

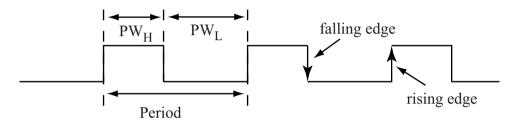

An important signal in a sequential logic circuit is the *clock* signal, whose waveform and associated definitions are shown in Figure 1.18. The following definitions are used in reference to clock waveforms:

- A *rising edge* is a transition from low to high; a *falling edge* is a transition from high to low.

- The *period* of a clock is the time in seconds (s) between two edges of the same type. A clock waveform typically has a fixed period; in other words, the period does not vary over time.

- The *frequency* of a clock is defined as 1/(period) measured in Hertz (Hz), where 1 Hz = 1/(1 s) (a 1 Hz clock has a period of 1 second).

- The high pulse width (PW<sub>H</sub>) is the amount of time the clock is high between a rising and falling edge, the low pulse width (PW<sub>L</sub>) is the amount of time the clock remains low between a falling and rising edge. The duty cycle is the percentage of time that the clock remains high.

Clock signal equations are summarized in Equations 1.3 through 1.7 as:

$$Frequency = \frac{1}{Period}$$

(1.3)

$$Period = \frac{1}{Frequency}$$

(1.4)

$$Duty\_cycle = \frac{PW_{H}}{Period} \times (100\%)$$

(1.5)

$$PW_{\rm H} = \frac{(\text{Duty\_cycle} \times \text{Period})}{100}$$

(1.6)

$$PWL = \frac{((100-Duty\_cycle) \times Period)}{100}$$

(1.7)

Figure 1.18, the clock waveform, is an example of a *timing diagram*, which is a method for describing time-dependent behavior of digital systems. In a timing diagram, one or more waveforms can be displayed, and time is assumed to increase from left to right. A *waveform event* is a change in waveform value. If waveform event *A* occurs to the right of waveform event *B*, then *A* occurs after *B* in time. The clock waveform shown in Figure 1.18 is an idealized view of a clock signal; an oscilloscope trace of an actual clock signal would reveal visible rise and fall times for clock edges, and perhaps ringing (small oscillations) on the end of rising and falling edges.

FIGURE 1.18 Clock signal definitions.

Table 1.4 lists commonly used units for time and frequency. A 1 kHz clock has a period of 1 ms, a 1 MHz clock has a period of 1  $\mu$ s, and so forth. Observe that kHz has a lowercase "k", where k = 1000; an uppercase K is reserved for the value 1024 (K = 2<sup>10</sup> = 1024). The suffixes M and G have values of 10<sup>6</sup> and 10<sup>9</sup>, respectively, when applied to time, frequency, and data transfer rate specifications (the values of M = 2<sup>20</sup> and G = 2<sup>30</sup> are used when referring to memory capacity). Timing and frequency specifications of digital circuits are contained in datasheets provided by the manufacturer. Time and frequency values are always specified using one of these units; in other words, a time is never specified as 1.05e–4; instead, it is specified as 105  $\mu$ s.

#### TABLE 1.4 Common Units for Time and Frequency

| Time                                          | Frequency                              |

|-----------------------------------------------|----------------------------------------|

| milliseconds = $ms = 1e10^{-3} s$             | kilohertz = $kHz = 1e10^3 Hz$          |

| microseconds = $\mu$ s = 1e10 <sup>-6</sup> s | megahertz = MHz = 1e10 <sup>6</sup> Hz |

| nanoseconds = $ns = 1e10^{-9} s$              | gigahertz = GHz = 1e10 <sup>9</sup> Hz |

Sample Question: A clock has a duty cycle of 40%, and a frequency of 19.2 kHz. What is the period and low pulse width, in microseconds?

Answer: The period is  $1/(19.2 \text{ kHz}) = 1/(19.2 \text{ e}10^3) = 5.21\text{e}10^{-5} \text{ s}$ . To convert this value to microseconds, do a unit conversion via:  $5.21\text{e}10^{-5} \text{ s} * 1 \text{ } \mu\text{s}/100^6 \text{ s} = 52.1 \text{ } \mu\text{s}$ . PW<sub>L</sub> = ((100–Duty\_cycle) \* Period)/100 = ((100–40) \* 52.1 \text{ } \mu\text{s}) / 100 = 31.3 \text{ } \mu\text{s}.

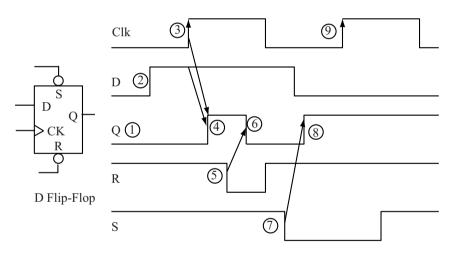

### The D Flip-Flop

There are many varieties of sequential logic elements. In this section, we review only the dominant type used in digital logic design, the *D Flip-Flop* (DFF). A DFF, as seen in Figure 1.19, can have the following input signals:

**CK** (**input**): The clock input; the arrival of the clock *active edge* sets the internal state of the DFF equal to the data input if the asynchronous inputs R, S are negated. The rising clock edge is the active clock edge for the DFF in Figure 1.19; it is said to be *rising-edge triggered*. A *falling-edge triggered* DFF has a bubble on its clock input.

**D** (input): The data input; the internal state of the DFF is set to this value on the arrival of an active clock edge if the asynchronous inputs R, S are negated. The D input is said to be a *synchronous input* as it can only affect the DFF on arrival of an active clock edge.

**S** (input): The set input; the internal state of the DFF becomes a "1" when this input is asserted. In Figure 1.19 this is a low-true input, so a low voltage on this input asserts set. This input is said to be *asynchronous* as its operation is independent of the clock input.

**R** (input): The reset input; the internal state of the DFF becomes a "0" when this input is asserted. In Figure 1.19 this is a low-true input, so a low voltage on this input asserts reset. This input is also an asynchronous input.

Q (output): The Q output is the value of the internal state bit.

Not all DFFs have S and R inputs; all DFFs have at least CK, D, and Q. The timing diagram in Figure 1.19 contains the following sequence of events:

- 1. The initial value of the DFF state bit is "0" as reflected by the Q output.

- 2. The D input becomes a "1", but this has no effect on the Q output as a rising clock edge has not occurred.

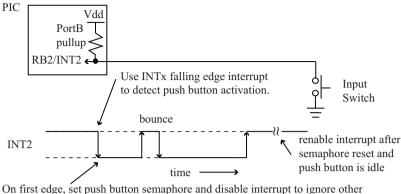

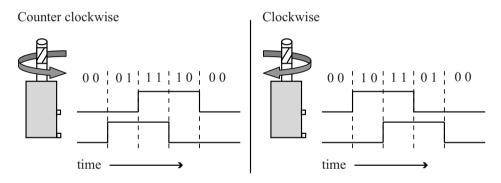

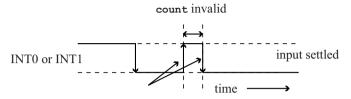

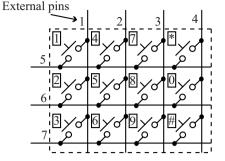

- 3. A rising clock edge arrives.